数字化中频(DIF)频谱剖析仪在高中频完结数字化处理,具有剖析带广大、RBW小、丈量时长短,可对杂乱信号施行时—频剖析的功用,因而得到越来越广泛的使用。但因为现有的数字信号处理器(DSP)处理速度有限,往往难以对高速率A/D采样得到的数字信号直接进行实时处理。为了处理这一对立,需求选用数字下变频(DDC)技能,将采样得到的高速率信号变成低速率基带信号,以便进一步的剖析处理。用现场可编程阵列(FPGA)来规划数字下变频器有许多优点:FPGA在硬件上具有很强的稳定性和极高的运算速度,在软件上具有可编程的特色,能够依据不同的体系要求,选用不同的结构来完结相应的功用,具有很强的灵活性,便于进行体系功用扩展和功能晋级。

数字下变频

数字下变频的首要意图是经过数字混频将A/D转化输出的中频信号搬移至基带,然后经过抽取,滤波完结信道提取的使命。因而,数字下变频器由本地振荡器(NCO)、混频器、抽取滤波器和低通滤波器组成,如图1所示。

图1 数字下变频原理图

A/D改换后的信号分红两个信号,一个信号乘以正弦序列(同相重量),下变频至零中心频率上,经过抽取滤波器、整形低通FIR滤波构成与原信号相位相同的信号;另一路信号乘以经过90度相移的正弦序列(正交重量),同样是下变频至零中心频率上,再经过相同的抽取滤波器、整形低通FIR滤波器,构成与原信号正交的信号。这样,DDC输出的低速率、零中频的正交的两路信号送往DSP等数字信号处理器进行后续的数字处理。

DDC的FPGA

以某中频数字化接收机为例来阐明怎么完结依据FPGA的数字下变频器。输入信号为中频26MHz,带宽500KHz的调频信号,该信号经过A/D改换之后送到DDC(A/D采样精度为8位,采样率20MHz),要求DDC将其改换为数字正交基带信号,并完结10倍抽取,即输出给基带处理器的数据速率为2MSPS,最终再经过16阶FIR滤波器进行信号整形。

NCO的完结

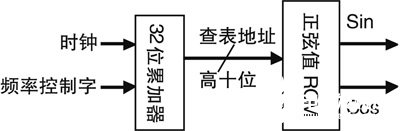

NCO选用直接数字组成(DDS)的方法完结,现在常见的技能有查表法和CORDIC计算法,本规划选用查表法来完结NCO,其原理图如图2所示。

图2 NCO原理图

32位累加器由一个32位的加法器和一个32位寄存器组成,在时钟的效果下,加法器经过寄存器将输出数据送入到加法器的一个输入端,与32位的频率操控字进行相加运算,得到一个有规则的相位累加成果。因为正弦值在一个周期内取有限个采样值,大于2pi部分的正弦值仅仅这有限数值的重复呈现,因而,当累加成果大于FFFFFFFFH是,不需发生进位,而是从头从00000000H开端累加。为了减小ROM的容量,依据相位切断技能,取累加器输出的高10位作为查表地址,可是这种完结方法,在下降成本的一起,也引入了杂散重量,影响了NCO的纯度。正弦值ROM中存储的是预先计算好的正弦波幅值,使用正弦波的对称特性,只需存储四分之一周期的幅值,再经过相应的转化即可恢复出整个周期的幅值。一起,因为余弦波和正弦波相位差为pi/2,能够很简略的完结余弦信号。其要害部分的VHDL代码如下:

process

begin

wait until clk=’1’;

if add(8)=’0’ then

address《=add(7 downto 0);

else

address《=”11111111”-add(7 downto 0);

end if;

if add(9)=’0’ then

qou(7)《=’0’;

qou(6 downto 0)《=q;

else

qou(7)《=’1’;

qou(6 downto 0)《= ”1111111”-q;

end if;

end process;

抽取滤波器的完结

CIC积分梳状滤波器是完结高速抽取十分有用的单元。CIC滤波器的体系函数为:

![]()

式中D即为CIC滤波器梳状部分的推迟,滤波器系数都为1。从上式能够看出CIC滤波器的完结十分简略,只要加减运算,没有乘法运算,FPGA完结时可到达很高的处理速率。可是,单级CIC滤波器的旁瓣电平只比主瓣低13.46dB,这就意味着阻带衰减很差,一般是难以满意有用要求的。为了下降旁瓣电平,能够采纳多级CIC滤波器级联的方法处理。在CIC滤波器的完结过程中,需求给内部寄存器供给满足的位宽,其计算公式为:

![]()

其间N为级数,M为推迟,R为抽取倍数。

本规划中,CIC滤波器需求完结10倍的抽取,选用4级级联来完结,因为输入、输出数据均为8bit,故内部寄存器所需的最大位宽为,旁瓣容限可到达4×13.46=43.44dB。

CIC滤波器完结的要害是抽取器的分频规划,其VHDL代码如下:

signal count : integer range 0 to 9;

signal clk2 : std_logic;

if (count=9) then –抽取器分频完结

clk2《=’1’;

else

clk2《=’0’;

end if;

comb : process –抽取器代码

begin

wait unTIl clk2=’1’;

i3d1《=c0;

…………

c4《=c3/2-c3d1;

end process comb;

低通滤波器的完结:

数字下变频器的最终一个模块是低通FIR滤波器,首要用来对信号进行整形滤波,消除信号中存在的噪声。本规划选用并行结构的FIR滤波器,由2个8阶滤波器级联完结16阶的滤波器,由预相加模块、查找表模块和移位相加模块组成,结构图如图3、4所示。

这种结构的滤波器结构简略、易于完结,很简略扩展成高阶滤波器。首要经过MATLAB中的FirDesignTool东西得到滤波器的系数图表(表1)。使用线性FIR滤波器抽头系数的对称性,经过加法器将对称的系数进行预相加,然后下降硬件规划。依据分布式算法原理,经过将抽头系数的一切或许组合固化在ROM中,使用查找表来替代乘法器。使用预相加模块发生的地址来查找ROM表,并将相应的数值进行移位相加,然后得出正确的成果。

表1 16阶FIR滤波器系数

DDC体系的完结

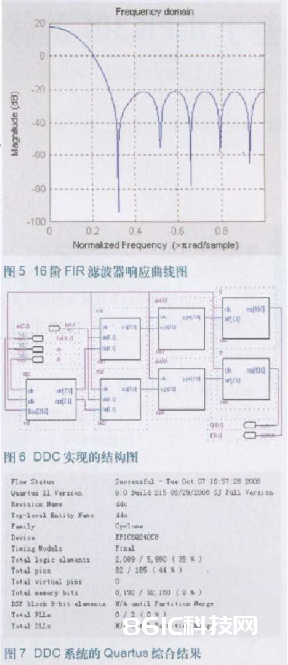

使用上述的各个模块,可得到DDC体系的完结结构图如图6所示。

整个体系在Cyclone系列芯片EP1C6Q240C8上完结,其FPGA归纳成果图7所示。

时序测验图(图8)中,黄色为体系时钟波形,绿色为NCO发生的正弦波时序波形,蓝色为抽取滤波器输出的时序波形,粉红色为FIR滤波器输出时序波形。从示波器显现的时序图能够看出抽取滤波器输出波形的延时最大,大约为14ns左右,这和软件仿真的成果比较符合,仿真中抽取滤波器输出的延时为16.47ns。故抽取滤波器是限制体系时钟速率进步的要害因素。

结语

本文介绍了一种使用于数字化中频频谱剖析仪的数字下变频电路,整个电路依据FPGA完结,结构简略,易于编程完结。

责任编辑:gt