作者:泰克科技运用工程师 李煜

PCIe接口自从被推出以来,现已成为了PC和Server上最重要的接口。为了更高了数据吞吐率,PCI-SIG安排不断改写接口标准,从PCIe 3.0的8GT/s数据速率,到PCIe 4.0的16GT/s数据速率,再到PCIe 5.0的32GT/x。PCI-SIG安排完结了在速率翻倍的一起,仍能坚持运用一般的FR4板材和廉价接插件,首要源自两个方面的改善,一是运用128b/130b编码来替代8b/10b编码,使得编码功率大幅进步;另一个是运用动态均衡技能,来替代从前代的静态均衡技能。

这儿聚集于PCIe 3.0和4.0中的动态均衡技能,介绍其原理、完结及其相关的一致性测验。这样一种动态均衡技能,在spec中被称作“Link Equalization”(链路均衡,简称为LEQ)。本系列文章分上下两篇,本文理论篇首要介绍PCIe 3.0/4.0的链路均衡的作业原理,下一篇实践篇则侧重于链路均衡的测验和调试。

别的,泰克PCI Express专家David Bouse将在4月10日(周五)13:00-16:00直播讲堂【PCI Express 5.0标准更新解读和测验揭秘】解说怎么处理PCIe 5.0的新测验应战https://info.tek.com/cn-pcie-mofu.html。

PCIe 3.0 & 4.0的链路均衡

在PCIe 3.0和4.0中的链路均衡技能相较于从前代要杂乱得多,这样一种动态均衡技能可以分为两个方面进行评论。

- 均衡特性方面:从这个方面来说,相关于从前代的均衡来说,3.0和4.0中的均衡技能的硬件功能指标要求更高了。

- 协议方面:为了完结动态地调整均衡设置,需求协议层的合作,这是经过PHY层的LTSSM状况机中的Recovery.EqualizaTIon子状况来完结的。

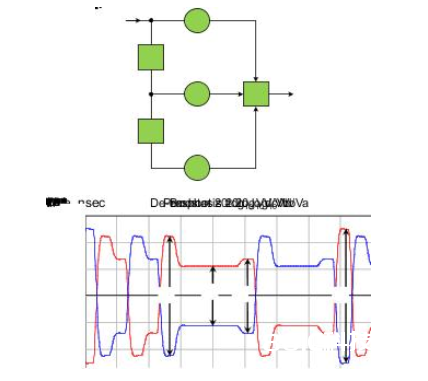

先来从均衡特性的视点来看看PCIe 3.0和4.0的均衡,如下展现了在PCIe 3.0/4.0中所运用的悉数均衡技能,在Tx端有FFE(Feed Forward Equalizer,前馈均衡器);在Rx端有:CTLE(ConTInuous TIme Linear Equalizer,接连时刻线性均衡器)和DFE(Decision Feedback Equalizer,判定反应均衡器)。经过FFE和CTLE,可以去除大部分由ISI所引进的颤动;经过DFE可以进一步去除ISI,它还能去除部分的阻抗失配所构成的反射。经过这些均衡处理,就可以最大程度上地确保在接纳端判定输入处将眼图翻开。

除了上述这些均衡特性上的支撑外,在协议层(LTSSM)中还规则需求经过协议的方法来动态调整链路上的均衡设定值,这整个进程称作链路均衡(Link EqualizaTIon,LEQ)。在链路均衡进程中:

- 本地端依照某个初始Tx EQ的设定来发送数据;

- 对端在接纳到数据时,会依据误码率或信号质量来判别该Tx EQ是否适宜;

- 若不适宜,对端会经过协议向本地端恳求一个新的Tx EQ值;

- 本地端在接纳到这个恳求值之后,会改动Tx EQ的值。

经过这一动态进程,就可以确保链路上的Tx EQ为最优值。与此一起,本地端和对端也会一起调整Rx EQ。经过动态地调整Tx EQ和Rx EQ,就可以灵敏地习惯不同的信道状况。

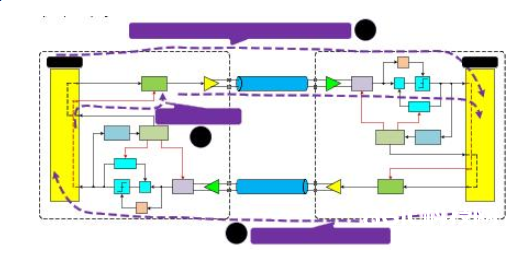

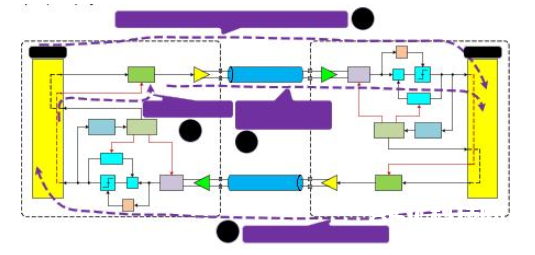

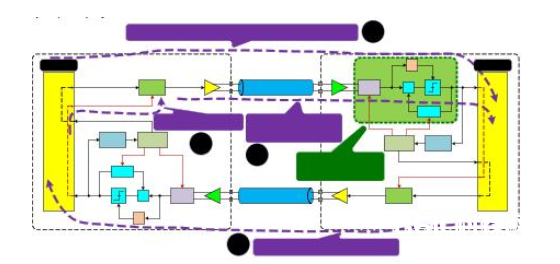

图1 LEQ硬件完结的模块框图

发送端的均衡:FFE

在PCIe 3.0 & 4.0中运用的都是3-tap FFE,如图 2a所示。其间,Qn为数字信号,建模时取值为±1;c-1, c0, c+1为FFE的抽头系数;voutn为发送端的模仿信号输出。

(a)FFE的模型框图 (b) FFE的模仿电压输出

图2 PCIe 3.0 & 4.0发送端所运用的3-tap的FFE

抱负状况下的差分电压起伏有:23÷2=4种或许性,这四个电压起伏在PCIe标准中(如图 2b所示)分别被符号为Va,Vb,Vc,Vd。

Va=c0-c+1+c-1×2g

Vb=c0+c+1+c-1×2g

Vc=c0+c+1-c-1×2g

Vd=c0-c+1-c-1×2g

其间,Vb被称作去加剧电压(de-emphasis voltage),Vc被称作预冲电压(preshoot voltage);Vd被称作最大起伏电压(boost voltage),PCIe标准中没有为Va取一个专门的姓名。在此根底上,标准中经过三组比值来齐备地描绘FFE的功能:

DEEMPHASIS=20logVbVa=20logc0+c+1+c-1c0-c+1+c-1

PRESHOOT=20logVcVb=20logc0+c+1-c-1c0+c+1+c-1

BOOST=20logVdVb=20logc0-c+1-c-1c0+c+1+c-1

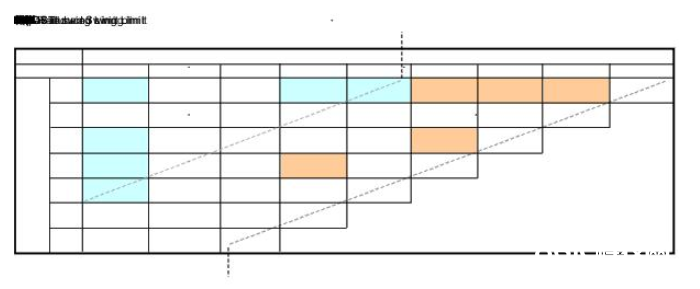

若不加约束的来说,那么c-1, c0, c+1构成的组合有无量多个。但并不是一切的组合在实践运用中都是适宜的。其间一个最重要的约束条件便是:去加剧电压Vb不能过小,过小的去加剧电压会导致输出信号在接纳端的眼高过低。因而经过BOOST比值对去加剧地电压幅值进行约束:关于满摆幅的Tx输出,标准要求BOOST≤9.5dB;关于减摆幅的Tx输出,标准要求BOOST≤3.5dB。终究会构成一个如图 3类似的矩阵表,图中系数的粒度为1/24。在实践运用中可所以其他的粒度值,例如1/64;更小的粒度可以使系数空间的取值或许性更多,在LEQ调节时也更精密。

图3 发送端均衡的系数空间的矩阵表举例

鉴于系数空间上的取值或许性较多,PCI-SIG协会在开发协议的进程中,广泛地研讨了在不同插入损耗下最优的系数取值组合;终究选定了若干个特定的系数取值组合,并把它们称作预设定值(preset),在实践的LEQ进程中,链路两边就可以先选用预设定值进行粗调;若还以为链路的均衡设置依然没有到达最优,可以进一步经过系数空间的方法进行细调,终究到达速度和精度的平衡。

接纳端的均衡:CTLE和DFE

在PCIe 3.0 & 4.0 根底标准中,并没有明确地规则接纳端的结构是怎样的;而只是从丈量的视点对接纳端功能进行了规则。相反地,在标准中界说了一个行为级CTLE和行为级DFE。这些行为级模型可以作为规划攻略;而且为了使得待测目标可以经过标准的要求,一般来说用户所规划的接纳端功能至少要等于这些行为级模型的功能,可以强于这些行为级模型,但不能弱于这些行为级模型。

(a) (b)

图4 行为级CTLE的频响曲线:(a) PCIe 3.0 (b) PCIe 4.0

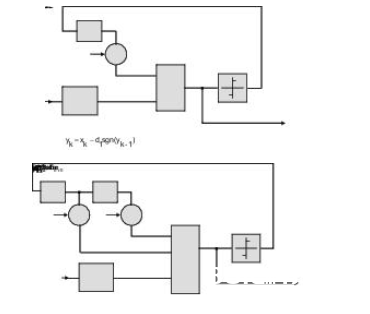

发送端的输出在经过一段很长的FR4走线之后,只是运用CTLE,或许是不行的。因而在PCIe 3.0 & 4.0中,还运用了DFE的技能。在3.0中,运用1-tap的DFE,而在4.0,因为速率相关于3.0翻倍了;所以运用2-tap的DFE,以便移除更大的ISI。

与线性均衡器FFE和CTLE比较,DFE为一种非线性均衡器。DFE的根本主意是:若现已正确接纳了之前的比特数据的话;那么从前的比特数据对当时比特所发生的影响便是已知的;然后咱们就可以经过反应的方法进行补偿,这样就可以进一步消除颤动和噪声的影响。不难看出这儿的非线性体现在:反应回来的信号是经过判定之后的数字信号;而判定电路是一种非线性电路。明显,反应通路上的抽头数目越多,那么对颤动和噪声的消除或许就越好;这也便是为什么3.0中运用1-tap的DFE,而在4.0中运用2-tap的DFE。

(a) (b)

图5 行为级DFE的结构:(a) PCIe 3.0 (b) PCIe 4.0

链路均衡进程

链路上的两头刚开端树立通讯的时分,并不知道整个信道的物理特性是怎样的,例如插入损耗多大,是否有阻抗不接连等。因为PCIe 3.0和4.0的插入损耗答应的改变规模很大,一个静态的均衡设置并不能掩盖一切的状况。这样就需求链路上的两边依据当时物理信道的特性,来动态地调整均衡设置,使得均衡设置关于当时的物理信道来说是最优的。假定Port A和Port B是一个链路上的两头,那么链路均衡进程要做的作业有:

- 装备Port A和Port B的初始均衡设置;

- 装备从Port A Tx à Port B Rx这一方向的均衡设置;

- 装备从Port B Tx à Port A Rx这一方向的均衡设置;

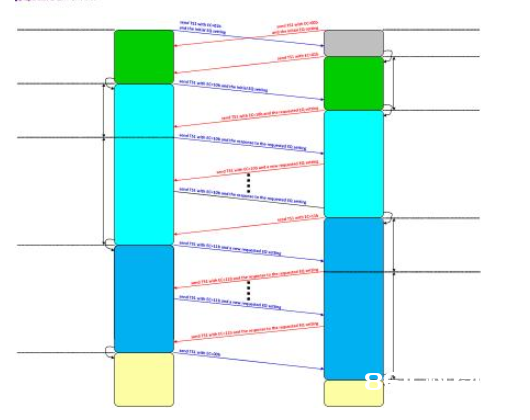

下面咱们以Port A Tx à Port B Rx这一方历来阐明链路均衡时怎么完结的。如图 6所示,在8GTs/或许16GT/s速率下的链路开端树立通讯时,是以初始的未优化的TX EQ在发送TS1/TS2序列,而且Port A在TS1/TS2序列中标明其所用的TX EQ的值。

图6 LEQ: 本地端发送未经优化的初始TX EQ

当Port B Rx在接纳到这些TS1/TS2序列时,芯片内部存在一块电路或许一套算法来评价当时的TX EQ是否适宜,若以为不适宜,就会如图7所示,发送TS1序列来恳求一个新的TX EQ。

图7 LEQ:对端恳求一个新的TX EQ

随后,Port A会接纳到恳求设置TX EQ的TS1序列,如图8所示,调整其TX端的FFE的设置。

图8 LEQ:本地正确地接纳到了对端的恳求,设置新的TX EQ

Port A在调整完Tx FFE的设置之后,如图9所示,会将新的TX EQ设置值更新到TS1/TS2的序列之中,发送到Port B端。若Port B依然觉得这个时分的TX EQ不是最优,那么依然会重复图中的2~4进程,直到到达最优的TX EQ。当然上述进程并不能无限进行下去,有必要要在大约32ms的规模进行完。

图9 LEQ:本地端奉告对端已成功设置新的TX EQ

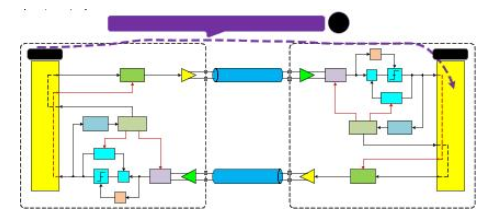

在上述2~4进程的一起,Port B的RX端也在不停地调整其RX EQ,如图 10所示。如图6~图10中所评论的,LEQ是依据恳求-呼应机制来完结动态均衡的。在PCIe的标准中,LEQ一共包括四个阶段:Phase 0、Phase1、Phase 2、Phase 3。其间上行端口包括悉数四个进程;而下行端口不包括Phase 0。

图10 LEQ:整个进程中一起调整RX EQ

经过图11不难看出,在LEQ进程中,上行端口和下行端口的行为是有差异的。以上描绘的是在LEQ进程中链路上的两边怎么调整Tx EQ。而关于Rx EQ,依据Base标准中的阐明,在整个LEQ的进程、以及在后续正常作业的进程中,链路两边都可以一向调整Rx EQ。

图11 LEQ的状况跳转示意图