从大学年代第一次触摸FPGA至今已有10多年的时刻。至今记住最初第一次在EDA试验平台上完结数字秒表,抢答器,密码锁等试验时,那个振奋劲。其时因为没有触摸到HDL硬件描绘言语,规划都是在MAX+plus II原理图环境下用74系列逻辑器材建立起来的。后来读研究生,作业陆陆续续也用过Quartus II,Foundation,ISE,Libero,并且学习了verilogHDL言语,学习的过程中也渐渐体会到verilog的妙用,本来一小段言语就能完结杂乱的原理图规划,并且言语的移植性可操作性比原理图规划强许多。

在学习一门技能之前咱们往往从它的编程言语下手,比方学习单片机时,咱们往往从汇编或许C言语入门。所以不少开端触摸FPGA的开发人员,往往是从VHDL或许Verilog开端下手学习的。但我个人认为,若能先结合《数字电路根底》体系学习各种74系列逻辑电路,深刻了解逻辑功用,关于学习HDL言语大有裨益,往往会起到事半功倍的作用。

当然,任何编程言语的学习都不是一朝一夕的事,经历技巧的堆集都是在点滴中完结,FPGA规划也无破例。下面就以我的切身体会,谈谈FPGA规划的经历技巧。

1)看代码,建模型

只要在脑海中建立了一个个逻辑模型,了解FPGA内部逻辑结构完成的根底,才干了解为什么写Verilog和写C全体思路是不一样的,才干了解次序履行言语和并行履行言语的规划办法上的差异。在看到一段简略程序的时分应该想到是什么样的功用电路。

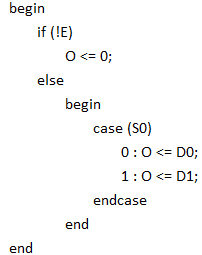

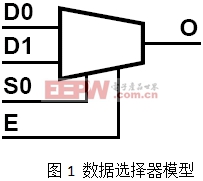

例如:

上面这段代码完成的功用便是一个带使能端的2选1数据选择器,如下图所示。

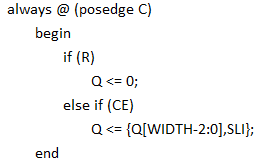

再例如: