频率组成技能起源于二十世纪30年代,其时所选用的频率组成办法是直接频率组成。它是运用混频、倍频、分频的办法由参阅源频率通过加、减、乘、除运算,直接组合出所需求的的频率。它的长处是捷变速度快,相位噪声低,但由于结构杂乱,价格昂贵,很快被筛选。在此之后呈现了直接频率组成。这种办法首要是将相位反应理论和锁相环技能运用于频率组成范畴,即所谓的PLL频率组成技能。PLL频率组成技能克服了直接式频率组成的许多缺陷,特别是它易于集成化,使得体积小、相位噪声低、杂散按捺输出频率高,但它的频率切换时刻相对较长。跟着数字信号理论和超大规模集成电路的开展,在频率组成范畴诞生了技能性的革新,那便是直接数字频率组成技能(direct digital synthesis,DDS)。这是一种频率组成的新办法,频率转化时刻短、频率分辩率高、输出相位接连、操控灵敏便利,但其频率上限较低且杂散较大,极大的约束了DDS的推行和运用。跟着电子技能的开展,各类电子体系对信号源的要求越来越高,怎么按捺DDS输出信号中杂散也就成了研讨热门。本文给出了几种按捺杂散的办法,关于运用DDS技能进行工程设计具有必定指导作用。

1 DDS的作业原理[1]

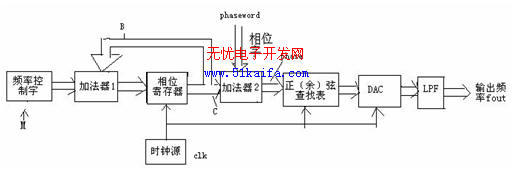

DDS作业结构如图1所示:

图1

DDS体系的中心是相位累加器,它由N位加法器与N位相位寄存器构成,相似一个简略的计数器。每来一个时钟脉冲,相位寄存器的输出就添加一个步长的相位增量值,加法器将频率操控数据与累加寄存器输出的累加相位数据相加,把相加成果送至累加寄存器的数据输端。相位累加器进人线性相位累加,累加至满量时发生一次计数溢出,这个溢出频率即为DDS的输出频率。正弦查询表是一个可编程只读存储器(PROM),存储的是以相位为地址的一个周期正弦信号的采样编码值,包含一个周期正弦波的数字起伏信息。将相位寄存器的输出与相位操控字相加得到的数据作为一个地址对正弦查询表进行寻址,查询表把输人的地址相位信息映射成正弦波起伏信号,驱动DAC,输出模拟信号;低通滤波器滑润并滤除不需求的取样重量,以便输出频谱纯洁的正弦波信号。

任何频率的余弦波形都可以看作是由一系列取样点组成。设采样时钟频率为fc余弦波每一周期由K个采样点组成,则该余弦波的频率为

设存储器中存了K个数据,(一个周期的采样数据),若相位累加器的步进值为M,则每周期的采样点数为K/M,输出频率为

假定相位累加器为N位,且悉数用刁难存储器的寻址,则

这便是DDS方程,依据取样定理  ,所以

,所以  。实践中一般

。实践中一般

一般情况下为了进步波形相位精度N取值较大,假如直接将N悉数作为波形存储器的地址,则需求极大的存储容量,实践中一般只取N的高位作为地址而省去低位。这样的做法不会引起输出频率分辩率的下降,但会使波形幅值发生变化,这样的差错称为切断差错,在接下来的章节里将进行具体评论。

2 DDS杂散特性剖析

DDS的数字化处理表现了频率捷变速度快、相位接连、易于编程操控等许多优异功用,但一起全数字化结构也带来丰厚的杂散。DDS的杂散首要来自三个方面:

●相位切断引进的杂散

●存储器的起伏量化差错

●DAC转化差错

下面逐个给予介绍。

2.1 相位切断引进的杂散

在DDS中,一般相位累加器的位数N大于ROM的寻址位数P,因而累加器的输出寻址

其N一P个低位就有必要舍掉,这样就不可避免地发生相位差错,称为相位切断差错,表现在输出频谱上便是杂散重量。由于 DDS输出信号通常是正弦信号,因而它的相位切断具有显着的周期性。这相当于周期性的引进一个切断差错,终究影响便是输出信号带有必定的谐波重量。相位切断并不是每个输出点都发生杂散。它们的巨细取决于三个要素:累加器的位数N,寻址位数P,频率操控字FCW。杂散重量散布在基频两头,是DDS杂散的首要来历。

2.2 起伏量化引进的杂散

由于DDS内部波形存储器中存储的正弦起伏值是用二进制表明的,关于跳过存储器字长的正弦起伏值有必要进行量化处理,这样就引人了量化差错。起伏量化首要有两种办法,即舍入量化和截尾量化,实践中DDS多选用舍入量化办法。一般地,起伏量化引人的杂散水平低于相位切断和 DAC非抱负转化特性所引起的杂散水平。

2.3 DAC转化引进的杂散

DAC转化带来的杂散首要包含DAC非线性带来的杂散和DAC毛刺引起的杂散。由于DAC非线性的存在,使得查找表所得的起伏序列从DAC的输入到输出要通过一个非线性的进程,加之DDS是一个采样体系,发生的谐波重量会以采样频率为周期搬移。别的,DAC的有限分辩位数,D/A转化进程中的瞬间毛刺,时钟走漏,转化速率受限等,也会在数模转化中发生了很多杂散频率重量。

3 改进DDS杂散的办法

全数字结构给DDS带来输出带宽和杂散的缺乏。现在,下降DDS输出杂散的办法首要有以下几种:

3.1 选用颤动注入技能

由前面的剖析可知,相位切断差错给输出信号引进了周期性的杂散,因而设法损坏杂散的周期性及其与信号的相关性,可以有效地按捺相位切断带来的差错。颤动注入技能是依据打破相位切断差错周期性的原理作业的,选用颤动注入后的杂散按捺可到达与添加2bit相位寻址相同的作用。颤动注入选用参加满意必定计算特性的扰动信号来打破差错信号序列周期性,将具有较大起伏的单根杂散信号谱线的功率在较宽的频率规模内进行均匀来改进总的信号频谱质量。依据颤动注入的方位不同,可有频率操控字加扰、R0M寻址加扰、起伏加扰,依据颤动注入的差错目标不同,由相位切断差错加扰和起伏量化差错加扰。C.E.Wheatly提出了一种针对相位切断差错的颤动注入办法,在每次累加器溢出时,发生一个随机整数加到累加器上,使相位累加器的溢出随机性的提早,然后打破周期性,按捺了杂散,但添加了背景噪声。

3.2 ROM起伏表紧缩

DDS是通过查表将相位转化为起伏值,假如可以将起伏表进行紧缩就相当于添加了R0M数据寻址位数,DDS输出频谱将进一步得到改进。各国学者对此进行了研讨并提出了各种紧缩算法,运用三角函数的恒等改换,将一个大的R0M分红几个小R0M,通过逻辑操控电路完成对sin 的近似。还可以运用弦信号的波形具有四分之一对称性,R0M表中只需存储[0,丌/2]的波形,在电路中运用相位的最高位操控输出波形的符号,次高位操控 R0M表的寻址,对相位和起伏进行恰当的翻转便可得到整周期波形,R0M表紧缩比4:1。在成功紧缩了R0M表的一起也带来了一些缺陷,如逻辑操控电路杂乱、实时性下降等。

3.3 PLL+DDS法

如前所述,DDS技能具有频率分辩率高,频率捷变速度快,变频相位接连等长处,但带宽和杂波按捺较差,而PLL频率组成技能具有宽带、高频率、频谱质量好,对杂散按捺较强等长处,但其频率捷变速度较慢。所以,在一些信号捷变速度、带宽,频谱质量要求相对折中的电路中,结合PLL频率组成技能与DDS 技能的结合,将是一种处理DDS杂散的抱负处理方案。

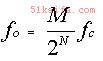

3.3.1 PLL+DDS频率组成原理

将DDS技能和PLL频率组成技能结合起来,用一个低频的DDS源鼓励一个PLL体系,用PLL环路将DDS信号倍频到高频信号,用滤波器滤除DDS输出信号杂波搅扰,然后使体系一起具有锁相环技能和DDS技能的长处,使输出的信号满意电路的需求。体系组成如图2所示

图2

3.3.2 PLL+DDS频率组成器中的杂散按捺

当DDS源驱动PLL锁相环时,由于PLL锁相环相当于一个高Q值的盯梢滤波器,其带宽一般不大于100KHz,所以DDS中的大部分杂散会被按捺的很好,然后DDS输出信号中的杂散违背主谱线间隔大于锁相环路带宽的杂散不会恶化。在PLL+DDS体系中,应依据DDS的原理挑选恰当的时钟频率和输出信号频率,使DDS输出信号与边端的杂散处于相对抱负状况,然后进步了体系的频谱纯度。

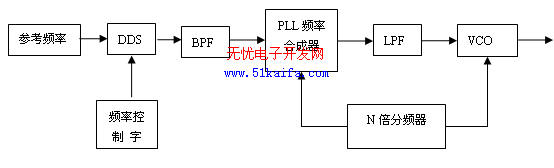

3.3.3 PLL+DDS频率组成器的完成

PLL+DDS频率组成器的组成如图3所示,下面介绍所选用的首要器材:

1. DDS部分

选用AD公司的AD9852高度集成化芯片,它选用了先进的DDS技能,结合内部高速、高功用D/A 转化器和比较器,构成可编程、可灵敏运用的频率组成功用。当提供给AD9852准确的频率时钟源时,AD9852将发生高安稳、可编程频率相幅的正弦波。 AD9852运用先进的CMOS技能,使得提供给这个高功用芯片的作业电压仅为3.3V。

2. PLL组成器部分

PLL组成器部分选用AD公司的ADF4106,它首要由低噪声数字鉴相器、准确电荷泵、可编程分频器、可编程A、B计数器及双模操控分频器等部件组成。数字鉴相器用来对R计数器和N计数器的输出相违进行比较,然后输出一个与二者相位差错成份额的差错电压。鉴相器内部还有一个可编程的推迟单元,用来操控翻转脉冲宽度,这个脉冲确保鉴相器传递函数没有死区,因而下降了相位噪声和引进的杂散。

图3

4 结束语

直接数字频率组成(DDS)是一种新式的频率组成技能,它代表了频率组成技能数字化开展的新方向。可是,DDS所固有的杂散和噪声,并且在频率升高时杂散和噪声也随之添加,使它的运用规模有必定的约束。所以怎么削减DDS输出中的杂散和噪声成分是当今DDS研讨中的中心问题之一。本文所介绍的颤动注入技、平衡DAC结构以及关于ROM起伏表紧缩的几种算法,都能有效地削减DDS输出信号中的杂散。特别当要求得到既有高的频率分辩率,又有较快的转化速度和较低噪声的高频乃至微波信号时,DDS+PLL技能就闪现出了较强的优越性,通过实践的工程运用,到达了令人满意的作用。总归,跟着现代科技的不断开展 DDS的功用会不断地完善,DDS运用范畴也会不断地拓宽。