可测验性规划 (DFT) 在市场上一切的电子规划主动化 (EDA) 东西中是最不被注重的,纵然在规划阶段进步芯片的可测验性将会大幅减缩昂扬的测验本钱,也是如此。最近的剖析数据标明,在制作完结后测验芯片是否存在制作缺点的本钱已增至占制作本钱的 40%,这已到达戒备水平。

DFT 可以下降经过问题器材的危险,假如终究在实践运用中才发现器材有缺点,所发生的本钱将远远高于在制作阶段发现的本钱。它还能防止除掉无缺点器材,然后进步良率。刺进 DFT 亦能缩短与测验开发相关的时刻,并削减测验安装好的芯片所需的时刻。

DFT 是电子职业的警钟,它选用主动测验形式生成器 (ATPG) 和存储内置自测验 (MBIST),是在芯片上刺进测验结构(例如扫描链、MBIST 结构或紧缩/解压逻辑)。扫描链经过串行移位寄存器添加了可控性和可调查性。凭借扫描链,测验电路的作业得到简化和减缩。运用 ATPG 东西主动生成测验形式可以削减耗时繁琐的测验向量创立使命。

当规划经过功用验证后,片上测验架构(或扫描链)会在门级的根底上被刺进,履行此操作时有必要小心翼翼,由于这或许会影响芯片的功用正确性。规划更改需求进行门级验证,以保证规划完好性未受影响。测验将由测验形式的长序列履行,这是一项核算密集型使命,比寄存器传输级 (RTL) 验证繁琐得多。

值得一提的是,从规划视点而言,创立并刺进 DFT 结构是一项非常简略的作业。不过,从密度和规划的层面来看,规划规划会添加,一起测验规划所需的测验形式数量也会使规划规划大大添加。

DFT 验证

当规划尺度到达数亿门时,根据软件仿真器的验证关于门级查看而言速度过于缓慢。DFT 办法只会让作业变得更糟。假如这些担负还可以敷衍,那么优先运用软件仿真阵列来推动流片有助于规划工程师的作业,但会为测验工程师带来阻止。芯片一般只进行很少的 DFT 验证就进行流片,而在流片后才履行完全的 DFT 测验,这时要修正规划缺点为时已晚。

DFT 验证具有多种形式,包含需求验证的自定义初始化形式。它可所以由主动测验形式生成器东西刺进的片上时钟操控器,这需求在形式履行期间进行动态验证;也可所以为 MBIST 添加的逻辑,这一般需求对测验形式的相关逻辑进行功用验证。SoC 或许包含一个自定义初始化形式,此形式可以装备测验并完结从功用形式到测验形式的转化。其他测验形式或许会选用低功耗技能,测验期间,芯片的一部分将进入低功耗形式,这就需求在恰当情况下的有用测验结构。

运用 DFT App 进行硬件加速仿真

硬件加速可以缩短履行完全 DFT 验证所需的仿真周期。一起还能验证各种规划和复杂性的芯片的功用。

30 年来,人们一向运用硬件加速仿真布置可重复编程的硬件来添加验证周期,而新的布置形式使这项技能成为更可行的验证东西,一起也为“App”的办法奠定根底。关于仍受困于根据软件仿真器进行验证的芯片规划团队而言,近期推出的一些硬件加速仿真运用程序无疑是个好消息。DFT App 可以加速需求进行全面门级仿真的芯片规划进程。凭借主动生成的形式,规划团队可以缩短整个形式开发周期。

这类硬件加速仿真的可扩展硬件和编译器可以对嵌入了扫描和其他测验结构的大型门级规划进行测验形式验证。它具有超卓功用,可以运转更多仿真周期,加速 DFT 剖析。DFT App 支撑职业标准 STIL 格式文件,可以与其他东西协同作业,STIL 文件可用于出产测验程序以便在制作过程中发现受损芯片。

用于硬件加速仿真的 DFT App 改变了硬件加速器在开发阶段的编译流程和运转时刻。这将为编译流程和运转时刻带来严重改变。具有扫描和 MBIST 结构的门级规划被载入硬件加速仿真的编译器。编译器创立了用于读取Stil文件中测验向量的测验结构,然后将这些向量运用到可归纳的待测器材 (DUT) 以及进行输出比较。编译器将用户网表从头编译并组成到一个可以兼容硬件加速仿真的结构化描绘中。编译器创立了用于读取Stil文件中测验向量的测验结构,然后将这些测验向量用到可归纳的待测规划上,再将网表从头编译并组成到一个可以兼容硬件加速仿真的结构化描绘中。测验操控架构还包含比较输出的机制。参见图 1。

图 1:经 DFT App 修改后的编译流程。

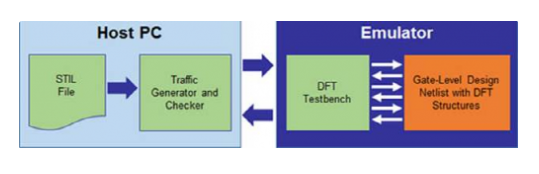

调用时,规划和测验渠道被映射到硬件加速器中。在运转期间,硬件加速仿真从 STIL 文件中提取测验向量,然后将其运用于 DUT 并比较输出,这一切都是以硬件加速仿真的速度完结。参见图 2。

图 2:显现主机 PC 和硬件加速器操作分化的运转时刻方框图。

DFT App 可履行完好的 DFT 验证形式设置,然后缩短形式开发周期。经过结合可处理多达数十亿个门的可扩展硬件加速仿真渠道以及支撑 DFT 办法的编译器,可以对已嵌入扫描和其他测验结构的大型门级规划进行测验形式验证。

完结芯片制作后,相同的 STIL 文件亦可以在测验车间运用。将测验向量载入 ATE,对芯片履行测验,并将呼应结果与 STIL 文件中的预期数值相比较。

可测验性规划

硬件加速仿真的履行速度比软件仿真高出几个数量级,而不是小幅添加。在硬件加速仿真中运转 DFT 形式时,某些衡量标准进步了四到五个数量级。参见表 1。

表 1:表现了功用改善的 DFT App 基准数据比照

关于软件仿真器一般需求三个月才干完结的测验,硬件加速仿真只需两小时就能完结,然后可在芯片流片前对测验向量和 DFT 逻辑进行完好验证。将 DFT App 运用于硬件加速仿真中,拓宽了运用方法、进步功用,并协助验证工程师躲避危险。凭借硬件加速器的强壮功用,DFT 工程师现在已能运用“App”来保证芯片合适进入制作流程。