1.介绍

LPHCSL(Low-Power HCSL)是为了下降传统的HCSL驱动器的功耗而开发的。LPHCSL的首要长处包含更好的驱动长线的功能,易于AC耦合,削减PCB板子面积,易于布线,下降资料本钱,本文将评论这些长处,重要的是要注意HCSL驱动器与LPHCSL驱动器对HCSL接纳器来说都是相同的。

2.HCSL驱动结构

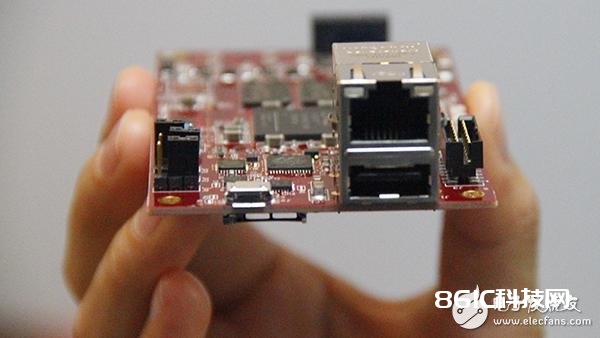

图1传统的和低功耗的HCSL驱动结构的比较

参阅图1的HCSL和LPHCSL输出结构图,传统的HCSL输出是经过操控正负输出差分对中的15mA电流,明显电源功耗为15mA * 3.3V约50mW。而LPHCSL不是选用传统的HCSL的电流驱动,而是选用推-拉(push-pull)电压驱动,电流耗费大约4到5mA。

图5和图6显现传统的HCSL与LPHCSL的终端匹配办法:

驱动器自身具有17欧姆的输出阻抗,所以,需求串联一个33欧姆的电阻,以获得与50欧姆传输线的匹配。关于传统的HCSL,为了防止呈现过度的振铃,串联电阻RS是必需求的。

某些接纳器片内或许有一个100欧姆的差分终端,这样的接纳器一般更常见,由于能够处理比较宽规模的起伏和共模电压,以及或许要去AC耦合的时钟信号,LPHCSL驱动器能够安稳驱动双终端(在源和接纳处都有终端电阻)。

从图6,咱们能够看得出LPHCSL并不需求对地的终端电阻。而由于功耗的原因,传统的HCSL驱动器不或许就将终端电阻集成到内部,尤其是芯片有许多输出的时分。很明显,LPHCSL相关于传统HCSL运用了更少的元件,下降了板子面积和资料本钱。

从原理上,传统的HCSL要求DC耦合,而LPHCSL并不要求DC耦合。咱们能够将AC耦合%&&&&&%串接到线路上,这样做并不会影响信号的摆幅和终端特点。而传统的HCSL运用AC耦合时,有必要细心考虑对地的DC途径,还或许需求额定添加元件。

PCIe时钟要求的上升速率为0.6V/ns到4.0V/ns,LPHCSL在驱动长线时能供给更高的上升速率。而传统的HCSL驱动取决于外部50欧姆终端来发生时钟的下降沿,这使得上升/下降匹配十分困难,由于仅时钟的上升沿受传统HCSL输出操控,而LPHCSL输出操控时钟的上升沿和下降沿,LPHCSL更快的上升速率对驱动长线时十分重要的。

3.定论

LPHCSL不只显著地下降了功耗,并且能更好地驱动长线,节约板子面积,削减本钱,更易于驱动AC耦合传输线,LPHCSL的运用会越来越广泛。

表1:传统的HCSL与低功耗的HCSL比较总结