在数字电路规划中,时钟信号是一种在高态与低态之间振动的信号,决议着电路的功用。在运用中,逻辑或许在上升沿、下降沿触发,或一起在上升沿和下降 沿触发。由于溢出给定时钟域的事例极多,故有必要刺进缓冲器树来足够地驱动逻辑。时钟树一般带有布线工程师有必要满意的推迟、歪曲率、最小功率及信号完整性 要求。

当电路早年工序规划人员转移到后工序布线工程师时,可以以为时钟概述与图表是有必要交流的最要害信息。多年以来,由于交流失误,数以小时、天乃至是星期计的规划作业沦为白搭,需求包括时钟树在内的全套从头组成。

在布线之前,选用极佳的时钟来用于组成及时序束缚。束缚的时钟界说或许呈现在模块的顶层焊盘或引脚;或许呈现在宏的输出,如锁推迟环(DLL) 或锁相环(PLL);或许作为发生的时钟呈现在除法寄存器上。这些时钟界说或许是也或许不是布线工程师需求界说时钟树根以在不同作业形式之间取得最优推迟 及平衡歪曲率的范畴。前工序及布线工程师之间环绕这些信息的高等级信息交流以及了解布线工程师怎样运用这些信息,将大幅优化物理规划流程的CTS进程。

有用CTS的规划技巧

下面的某些技巧在业界现已运用多年,但根据曩昔几年的经历,依然值得重复运用。

为时钟树根运用中到大强度的驱动器。这就使时钟树能有恰当的起点。但不要运用库中最大的驱动强度,假如信号完整性(SI)剖析或片上改变(VOC)剖析未呈现问题,可以在随后的规划中用到。

假如时钟除法寄存器及其同步寄存器要在独自测验形式中作业,保证它们被复用逻辑有针对性地驱动。这就可以在测验形式下在输入端添加推迟,而不会影响此功用形式下所发生的时钟驱动的其他一切寄存器。

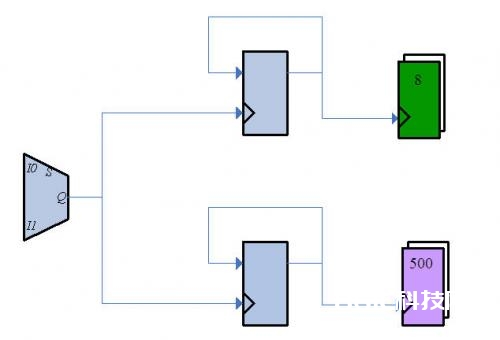

(divide-by)寄存器不会与任何下行寄存器平衡。绿色域的寄存器数量越少,越会使时钟速度比紫色域中的时钟速度快得多。

图1 寄存器时钟除法寄存器

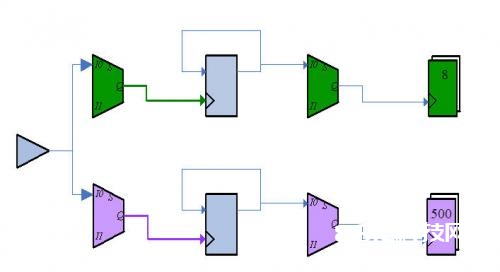

图2显现了或许使每簇下行寄存器及除法寄存器可以经过复用的一种输入具有极小时钟及经过复用的另一路输入具有平衡时钟的复用机制。

图2 下行寄存器及除法寄存器复用机制

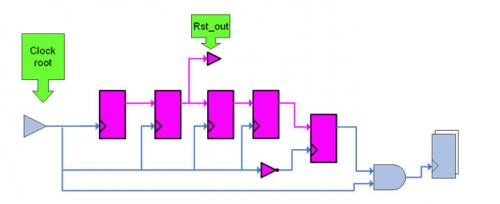

若有需求,则刺进专用复位驱动器。某些状况下将运用几个寄存器来同步复位。那些寄存器或许并不需求由相同的寄存器来平衡。在图3中,由于未选用会集战略,软件将测验平衡门控逻辑后的蓝色寄存器,而每个粉红色寄存器包括在复位同步逻辑中。

图3 平衡门控逻辑后的寄存器

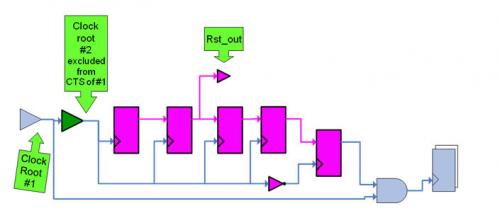

假如它们在各自专用驱动器中与其他寄存器分开了的话,在布线进程中这种状况就很简略处理。图4显现了可以怎样在规划交递(hand-off)交流进程中刺进及容易辨认占位符(place-holder)或扫除缓冲器,使布线工程师知道哪里或许会呈现平衡问题。

图4 刺进及容易辨认占位符或扫除缓冲器

供给超出预期的时钟图表及很多时钟简介。当时工序规划准备好供给网表进行布线时,他们现已十分了解规划及时钟要求。某些状况下,初始CTS规划 会提示预布线时序束缚中运用的抱负值在实践物理规划中不能实现的状况。假如供给了准确的时钟图以及带有时钟原理相关信息的网表交递,就可以更快地澄清导致 此状况的问题。

整体图或是代表规划中一切时钟(含门控逻辑)的图十分有用。这要么是选用画图软件,要么是运用电路图捕获东西等运用软件发生的图,乃至还可所以手绘并存储为%&&&&&%文档或发送传真给布线工程师的图。此图抵得上测验直接取得时钟格局的屡次通话或电子邮件交流进程中的千言万语。

由于图表或许会很杂乱繁琐,就需求供给相应的简介文档,包括发生的时钟、任何时钟门控或复用图画的概况以及歪曲率平衡和推迟要求等方面的阐释。 每种作业形式都需求这些详细信息,由于在刺进时钟树期间有必要应对每种形式。寄存器或许最后会供给用于功用形式的平衡,但假如咱们不细心的话,测验形式下可 能极不平衡。

假如时钟运用DLL或其他宏或它经过门控逻辑,这些详细信息就在所必需了。假如有需求的话,有或许经过那些类型的宏来组成及平衡。关于门控逻辑 而言,假如存在一个引脚经过一种形式来衔接、但同单元的其他引脚选用另一种形式来衔接的状况,走线东西将把这种状况辨认为“重会聚时钟”。尽管布线东西可 以处理这些问题,但更好的处理办法或许是迫使东西在时刻刺进期间检查这个引脚而非其他引脚。

业界软件东西中的CTS

业界软件遵从规划人员的标准及指引,以强壮的东西推进时钟树组成。源自前工序的跟时钟树根刺进点、推迟、歪曲率及过渡方针相关的信息以及用于门 控逻辑、经过寄存器和跨域联系的详细信息可以直接移植到CTS东西中。然后布线工程师将自已判别要运用的缓冲器类型、优化迭代及距离、屏幕和金属层等布线 要求。

在刺进时钟树之前,可以运用走线来保证存在旨在用于平衡的端点。还可以提示及评价门控逻辑、时钟树根扫除的分支、IO端点以及重会聚实例。

时钟树或许仅包括缓冲单元或是系列反相器。现在的大多数技能具有特别的时钟缓冲及时钟反相单元,这些单元供给平衡的上升及下降时刻,以协助保证占空比不被损及。还可以整合其他要求,如时钟树中等级或各个时钟单元的最大扇出。

定论

除了上文讨论的一切要素,布线工程师很或许还会测验有时钟门控认识的布局、时钟布线指引及平面布局调整。CTS代替一般在很少调整歪曲率、推迟 及过渡方针的状况下运转。试错法协助供给极佳的和谐。假如前工序了解CTS怎么作业且在最开端就交流时钟结构,那么布线工程师将可以愈加称心如意地接手任 务。日程中本来方案用于CTS的时刻就可以用于微调及改进“你的时钟”,而非简略地测验将其刺进到“我的布线”。