跟着现代通讯技能的敏捷开展,信号的调制方法向多样化开展,解渊技能也随之不断向前开展。为了对高速大带宽的信号进行实时解调,现在许多的解调要害算法都是在高速硬件上用可编程逻辑器件(FPGA)实观,使用FPGA强壮的资源和实时处理才能来快速的完结信号的盯梢、确定和解调可是,依据硬件的完结计划和依据软件的计划比较,往往存在不能敏捷习惯调制款式改动的问题。为了有用斛决这个问题,笔者经过基下FPGA部分动态町重构技能,提出了相应的解决计划。

1 FPGA部分动态可重构技能介绍

从九零年代以来,跟着FPGA芯片技能的逐步老练和开展,FPGA在各个范畴中的使用逐步扩展,芯片内部的资源规划也成倍添加。可是,跟着FPGA容量的扩展,FPGA的规划和完结也逐渐呈现了下面的瓶颈问题:

1)FPGA芯片内部布线跟着规划复杂度的添加,布线的难度成平方添加,布线的时刻也成倍添加。

2)关于大容量的FPGA,为了确保规划时约好的功用,为了满意时序约束条件,终究完结版别的实践资源使用率反而下降。

3)大容量的FPGA一旦规划完结后,对其进行部分模块的调整和优化常常需求很长时刻。

在此上述这些原因的基础上,FPGA的重装备技能应需而生。FPGA重装备技能分为彻底重装备技能和部分动态可重构技能两种。其间FPGA彻底重装备技能便是经过FPGA外部的装备处理单元,经过对FPGA装备管脚的编程,来完结整个FPGA内容的切换,这种方法在现在现已得到了较为广泛的使用。而FPGA部分动态可重构技能是经过FPGA内部或外部的装备处理单元,对FPGA内部部分资源的时分复用,来完结FPGA内部部分模块的切换。

对这两种装备技能进行比较,能够看到FPGA部分动态可重构技能的优势在于以下这些方面:

1)进步了装备速度。彻底重装备需求装备整个FPGA的比特流文件,而部分动态可重构技能只需求装备相应模块的逻辑内容,文什巨细相差悬殊,在相同的装备时钟频率下,部分动态可重构技能的装备速度是彻底装备的几分之一或许几十分之一。

2)省掉了彻底装备后的复位、下达参数的流程。彻底重装备在装备完结后,整个FPGA处于初始状况,需求从头对接口进行初始化,并装备运转参数。而部分动态可重构技能不必进行大局复位,下达参数也只需求针对重构的模块。

3)保存了FPGA运转的中心成果和数据。彻底重装备很难保存FPGA运转的中心成果,假如外接DDR SDRAM等存储单元,也会由于接口的从头复位而导致数据紊乱,而部分动态可重构技能彻底不必忧虑这些问题。

部分动态可重构技能具有上述相对与彻底重装备技能的优势外,也和彻底重装备技能相同,具有低功耗和灵动性高的长处,而且具有长途加载功用,能够经过有线网络或许无线网络来完结超距环境下的FPGA功用改变。

部分动态可重构技能和彻底重装备技能比较,对FPGA规划人员的开发才能和规划才能要求更高,下面经过对一个简略的数字信号解调体系,来给出部分动态可重构技能的完结途径。

2 FPGA部分动态可重构技能的硬件完结计划

FPGA部分动态可重构的硬件完结如图1所示,为了确保FPGA装备的可靠性,本文选用了FPGA外部单元操控装备流程的完结方法。一个根本的完结结构除了被装备的FPGA外,需求有装备操控模块、装备接口模块和装备存储模块这3个部分。其巾装备操控模块一般由DSP、单片机、ARM处理器或许PowerPC挑选,主要功用是从装备存储模块或许外部接口中获取装备比特流文件,并在需求部分动态重构的时刻把装备比特流文件传送到装备接口模块。装备接口模块一般由FPGA或许CPLD完结,功用是接纳装备操控模块传输的装备比特流,进行相应的时序转化,发生满意FPGA装备时序的信号,然后对FPGA进行装备。装备存储模块一般是FLASH或许SDRAM,能够长时刻或许暂时保存多个装备比特流文件。

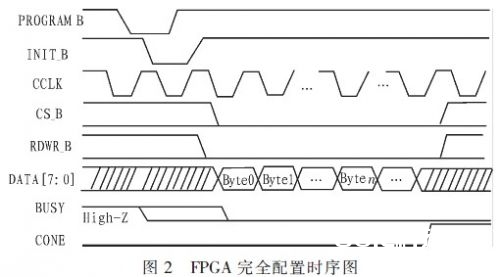

在图1的结构中,装备接口模块是完结的要害模块,依据装备速度和稳定性的要求,能够选用Slave SelectMap或许Slave Setial装备形式,从功用考虑,一般挑选Slave SelectMap这种并行装备形式,在装备时钟最高50MHz、装备管脚32位的情况下,装备速度能够到达1.6Gb ps。在Slave SelectMap形式下,装备接口模块和FPGA的管脚衔接能够参阅XilinxVinex-5 Configuration User Guide中相应章节,本文不再赘述。并依据如图2所示的装备时序,来完结FPGA彻底装备比特流文件的下载和功用完结。

在进行装备部分动态可重构比特流文件时,由于该比特流文件不像完好的装备比特流文件相同具有文件头,而是只要帧地址、装备数据及校验和,当一切装备内容传输到FPGA后,不会有DONE信号拉高来表明装备完毕。在这种情况下,有必要监督传输来的装备数据,当呈现部分重装备文件的完毕标志DESYNCH(0000000D)时,就能够判别部分重构流程完毕,能够运转新的重构模块。

3 依据FPGA部分动态可重构的信号解调体系开发流程

3.1 FPGA模块区分

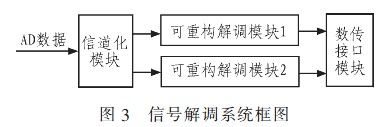

在完结了支撑FPGA部分动态可重构的硬件完结后,下面开端规划信号解调体系的FPGA规划架构。如图3所示,信号解调体系主要由信道化模块,可重构解调模块和数传接口模块组成。

信道化模块主要是把AD数据进行信道化处理,进行滤波,下变频、信道挑选和抽取。可重构解调模块是针对不同调制款式的别离完结不同的解调模块,并依据实践需求进行部分重构。数传接口模块是把解调的成果传输到FPGA外,进行后续处理和在界面中显现。

3.2 FPGA模块的规划和完结

依照图3所示的结构,依照下面过程进行依据部分动态可重构技能的FPGA程序规划:

1)把需求部分重构的FPGA模块规划为一个空盒,即只要输入输出管脚,没有实践内容的空模块。在进行空模块的管脚规划时要归纳考虑多种解调款式下的接口兼容性,确保一个模块接口能包括需求处理的一切款式。

2)别离完结不需求部分重构的FPGA予模块,并完结FPGA顶层模块。

3)对FPGA顶层模块进行归纳,发生顶层网表。

4)依照过程1)中的模块界说格局完结针对不同调制形式的解渊模块,如qpsk_demod,fsk_demod等,并经过仿真验证,然后逐模块别离归纳成独自的模块网表文件,保存到不同的目录中。

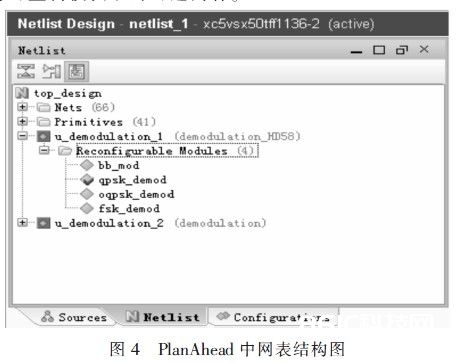

5)在PlanAhead东西中导入FPGA顶层网表,注意在导入选项中挑选支撑部分重构。在PlanAhead东西中把2个空的可重构解调模块设定为可重构分区(ReconfigurablePartition),如图4所示,并把过程4)中归纳好的模块网表指定为可重构模块下的可选内容。

6)在PlanAhead东西的Device视图中,对可重构模块区分分区(PBlock),现在分区只支撑矩形,要求分区包括的资源数目略大于解渊模块所需资源的最大值,其间包括逻辑资源(查找表和寄存器),乘法器(DSP48E)和RAM资源。

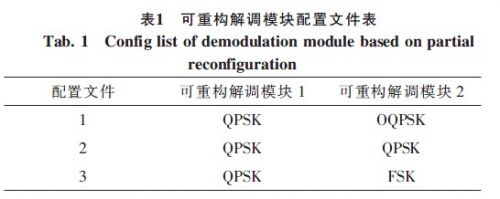

7)依据对2个可重构解调模块的不同装备,发生多个装备文件,装备文件的一个比如如表1所示,并逐个进行布局布线,发生完好的装备比特流文件和用于部分重构的比特流文件。关于每一组装备文件,会发生一个包括静态逻辑的完好装备比特流文件,和2个用于部分重构的比特流文件,别离对应2个不同的分区,装备加载时不能随意交换。

8)对表1中装备文件进行规划规矩查看比较,确保各组装备文件生成的完好装备的比特流文件是共同的。

9)完结以上规划后,首要调用恣意一个完好装备文件进行加载,确保FPGA成功运转静态逻辑,然后依据需求,挑选表1中的装备文件表中的任何1组,进行部分动态加载。

4 使用成果

以上规划经过实践验证,能够完结2路信号在不同调制款式的解调,当信号款式变化时,动态加载相应的解调模块,能够敏捷完结功用切换,完结对应的解调功用。经过实践测验,部分动态可重构模块的加载速度存10 ms以内,极大的进步了原有体系的功用。

5 定论

现在国际上对FPGA可重构技能的研讨极为广泛,本文介绍了一种依据Xilinx FPGA的部分动态可重构技能的信号解调体系,能够把不同的解调模块定位到芯片内部同一逻辑资源部分,经过重构这些资源来完结不同款式信号的解调,一起坚持其他部分电路功用正常运转,然后进步了体系的习惯才能。

本体系能够存通讯体系中得到使用,对航天、电力等范畴的相似体系也有参阅价值,能够进步相应体系的灵活性和扩展性,减低体系功耗,缩短体系开发时刻。