摘要:一种运用于轿车涡轮增压器叶片温度检测的双通道数据收集卡,该卡由峰值检测、串行A/D构成模仿电路和由FPGA构成整个数字电路而组成。要点规划了FPGA内部串并转化电路和FIFO,经仿真和试验验证,串并转化和FIFO的运用大大简化了收集卡的杂乱程度,进步了体系的可靠性和稳定性,在信号高速处理方面具有必定的运用价值。

0 导言

涡轮增压近年来是一个热门话题,早些年首要是群众轿车推出了一些涡轮增压车型,比方宝来、帕萨特车型就都是涡轮增压的典型代表。最近两年,涡轮增压有方兴未已之势,不只群众以及通用品牌推出了小排量的1.4TSI涡轮增压和1.6T涡轮增压动力,就连一些自主品牌也纷繁大打涡轮增压的好牌。

涡轮增压实际上是一种空气紧缩机,经过紧缩空气来添加进气量。它是运用发动机排出的废气惯性冲力来推进涡轮室内的涡轮,涡轮又带动同轴的叶轮,叶轮压送由空气滤清器管道送来的空气,使之增压进入气缸。当发动机转速增快,废气排出速度与涡轮转速也同步增快,叶轮就紧缩更多的空气进入气缸,空气的压力和密度增大能够焚烧更多的燃料,相应添加燃料量和调整发动机的转速,就能够添加发动机的输出功率了。

轿车上装置的涡轮增压器在全负荷作业状况下其转速可达每分钟8万到12万转。作业温度高达600~900℃,如图1。而涡轮叶片会发生1000℃的高温,能够说它的作业条件最为恶劣。

看到这些涡轮增压作业时的相片,就不难理解装备涡轮增压发动机的车为什么简单自燃了,这便是一块烧红的铁,不出事端则已,一旦燃油走漏,沾上高温作业中的涡轮增压器,瞬间高温会点燃汽油,继而导致爆破。为什么会发生这么高的温度呢?由于涡轮增压器温度=废气温度+涡轮快速滚动冲突温度+进气空气紧缩温度。不难理解涡轮烧红是正

常作业状况。改进这一作业条件的办法便是散热,涡轮本体内部有专门的机油通道(散热和光滑)和水道,经过油冷和水冷两层散热,下降增压器的温度。

1 双通道涡轮增压叶片温度收集卡

针对上述状况,对增压器散热特别重要,所以规划一套依据增压器作业温度不同而做相应调整的冷却体系。这套体系的难点在于对涡轮叶片温度的收集。在数据收集体系中一般选用并行数据总线办法进行操控信号传输和数据交换。在以往的规划中,很多运用中小规划集成电路及分立元件建立总线数据收集和操控功用模块,不只占用较大的印制板面积,并且规划作业量大,时序操控杂乱,收集速度不抱负。

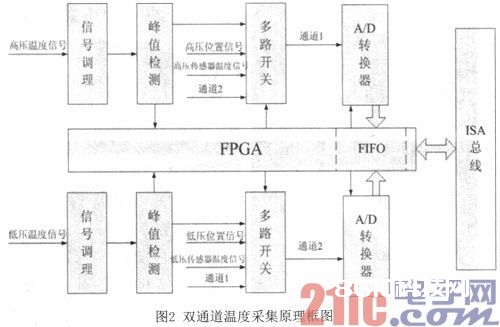

将FPGA运用到该体系的规划中能够有效地处理上述问题。FPGA能够完结许多中小规划%&&&&&%的功用,因而能够有效地削减印制板上功用模块的面积,一起削减体系体积。运用FPGA的在线编程和仿真功用能够模仿体系各类信号的时序,大大进步规划功率。所以规划了依据FPGA的双通道温度数据收集卡,原理框图如图2所示。整个收集体系分为收集模块、高速缓存模块、逻辑操控及接口模块三大部分。

收集模块由信号调度电路、双通道转化开关、A/D转化电路组成;高速缓存模块由FIFO及其操控电路组成,逻辑操控及接口模块由FPGA完结。双通道外部信号先进入调度电路,再经扩大、滤波等处理后,在经转化开关切换后,送到高速A/D进行数据转化。双通道模仿信号被次序转化为数字信号,并依照通道编号的不同在数据后附加通道信息存于FIFO中。整个进程由FPGA操控完结,并经过ISA总线与计算机通讯,运用FIFO答应两个端口一起拜访的功用,由计算机在高速收集进行的一起将已收集的数据取走,完结数据的高速接连收集。

2 收集卡的逻辑操控效果

2.1 依据FPGA的接连收集操控逻辑的完结

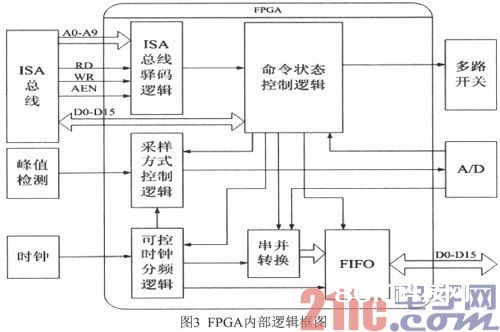

高速接连数据收集体系,需求A/D、高速缓冲及总线接口之间有杰出的时序匹配。针对这一问题,本文选用现场可编程逻辑门阵列(FPGA)来处理这一问题。选用FPGA之后不只大大进步了体系的可靠性,一起也很好地添加了体系的集成度。作为数据收集体系的操控中心,FPGA完结的逻辑功用有:发生A/D的作业时序、完结操控字所对应的功用、操控数据的存储和传输、供给总线的接口逻辑。其内部的逻辑模块能够分为时钟分频模块、传输操控及数据存储模块、总线逻辑接口模块三部分。FPGA对应的逻辑结构如图3所示。

指令状况操控逻辑是整个FPGA的指挥中心。它首要作业在于操控A/D转化进程、采样办法操控、时钟分频、串并转化和FIFO读写操控,使收集卡作业时独立于计算机,下降对体系资源的占用。这个进程中,时钟分频模块选用一个高精度时钟源经计数器分频得到的脉冲序列来完结采样办法操控、串并转化、FIFO读/写时钟操控,分频数由参数设置。传输操控及数据存储模块,由串行AD转化出来的数据经FPGA进行串行到并行转化,转化后的并行数据再送到FPGA内部FIFO存储单元中,以备计算机实时读取。总线逻辑接口模块完结整个收集体系同总线的数据交互。在这一模块中,经过地址译码,获取计算机的读写指令,并将这些指令传送给相应的逻辑模块和体系元件;选用锁存器加译码电路的办法,将计算机送来的操控字转化为详细的逻辑操控时序,完结其对应的功用。

2.2 串并转化

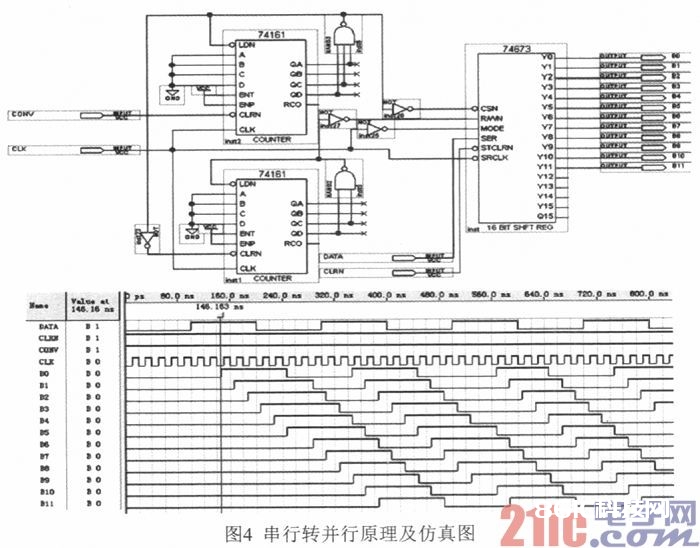

跟着芯片集成度和工艺水平的进步,串行A/D(特别是高精度串行A/D)转化芯片正在被广泛地选用。串行A/D转化芯片以其引脚数少(常见的8引脚)、集成度高(基本上无需外接其他器材)、价格低、易于数字阻隔、易于芯片晋级,本规划选用了BB公司出产的12位高速差分输入微功耗ADS7818,AD转化后的数据经光电阻隔后送入FPGA进行串行到并行转化后送到FIFO中。选用Quartus II图形规划输入办法,图4所示为串行转并行原理及仿真图。

16位串入并出移位寄存器74LS673,寄存器片选端CS的操控是由计数器74161计数13次为一次AD转化时刻开始的,R/W是由别一片74161计数12次来操控寄存器一次串行转并行读与写,SER是A/D转化的数据输入端。B0至B11的12位并行数据最终送到FIFOE中。

2.3 高速缓存

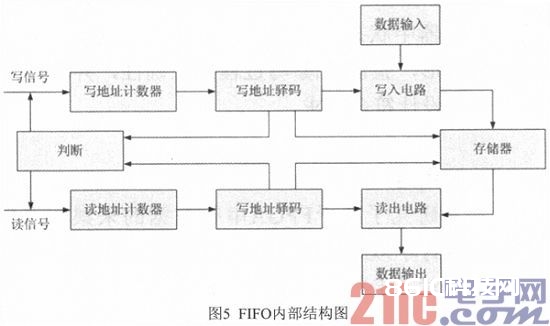

如何将A/D转化后的数据及时完整地经过总线传送给计算机,是能否完结高速接连收集的关键环节。选用FIFO高速缓存技能,能够很好地处理这个问题。FIFO常用于数据的缓存和包容异步信号的频率或相位的差异,运用FIFO能够在两个不同的时钟体系之间快速精确地传输实时数据。它是一种特别功用的存储器,数据以到达FIFO输入端口的先后次序顺次存储在存储器中,并以相同的次序从FIFO的输出端口送出,所以FIFO内数据的写入和读取只受读/写时钟和读/写恳求信号的操控,而不需求读/写地址线,其内部结构如图5所示。

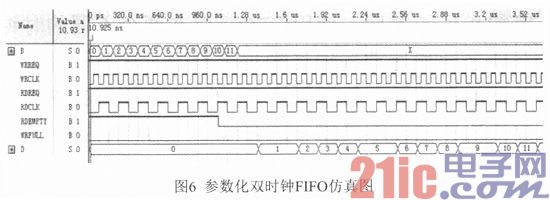

从硬件视点剖析,FIFO存储器实质是一块双端口数据内存,一个端口用于将数据存入FIFO;另一个端口用于将数据从FIFO中取出。FIFO的相关操作能够看作是2个指针的定位,写指针指向要写的内存部分,读指针指向要读的内存部分。FIFO操控器经过外部的读/写信号操控这2个指针移动,并由此发生FIFO空信号或满信号。所以硬件上来完结FIFO存储器,一般选用双端口的SRAM单元来存取数据。运用二进制计数器完结指针对SRAM的存储器地址的操作。异步FIFO存储器运用了2个时钟信号别离操控存储器的读操作和写操作,数据由某一个时钟域的操控信号写入FIFO,而由另一个时钟域的操控信号将数据读出FIFO。与同步FIFO存储器比较,它的读/写指针的改变由不同的时钟发生,是彻底独立的,因而其时序操控更为杂乱。本文直接调用其FPGA芯片内部可编程的底层硬件资源,完结高速异步FIFO存储器规划的思路和办法,提出了一种依据Altera公司的cyclone系列FPGA芯片,在OuartusII规划平台下,编译完结的高速异步FIFO存储器模型。图6所示为参数化双时钟FIFO仿真图。

读/写时钟异步使得FIFO存储器的输入和输出数据速率不相等,在读操作时钟频率高于写操作时钟频率时,或许呈现“读空”状况;当写操作时钟频率高于读操作时钟频率时,或许呈现“写满”状况。图6选取第2种状况进行仿真。从波形图中能够看到存储器中状况信号的改变进程,及输入和输出的数据波形,验证了读/写进程的正确性,异步FIFO存储器的规划符合要求。

3 结束语

本文研讨了依据FPGA串行数据的收集和存储技能,规划了双通道轿车涡轮增压叶片温度数据收集卡,并对该卡数据传输和存储进行了深化的研讨和仿真测验,成果均到达理论要求,到达了规划目标。本收集卡在整个冷却体系中具有无足轻重的位置,具有很好的运用远景。