摘要 多元阵天线阵列常被用于侦办和定位体系,相位差改变率则是单站无源定位中常用的观测参数。文中介绍了一种依据AD公司多片2.5 GSamplc·s-1的高速AD9739类型D/A转化器,选用DDS技能的多通道信号模仿器。经测验,该模仿器能较实在地模仿出,多元阵天线阵列所接纳到的宽带线性调频信号波形的相位差改变信息。

在工程测验中,为了查验体系的功用及其方针,一般需求向体系供应一个实在或仿真的信号辐射源,因为通用的信号发生器难以满意一些特定体系的要求,这就需求规划专用的信号模仿器。在某些定位体系的测验中,为了模仿多元天线阵列所接纳到的信号,需规划一种多通道的信号模仿器。

在现代雷达技能中,脉内宽带线性调频信号是研讨最早,运用最广的信号之一。而发生线性调频信号的办法首要有模仿法和数字法。模仿法一般是经过线性锯齿电压操控压控振荡器发生线性调频信号或运用SAW器材作为展宽网络发生调频信号。

跟着大规模集成电路的开展,DDS被广泛运用于宽带线性调频信号的发生,运用该技能能发生恣意波形,并能准确操控输出波形的频率、起伏和相位。现在,DDS法硬件计划首要有两种:一种是DDS SASIC芯片法,即运用DSP或FPGA给内部集成DDS核以及高速D/A转化器的DDS芯片送入操控字,可得到所需的信号;另一种是FPGA与高速D/A转化器结合,由FPGA完结DDS核的功用,送高速D/A转化器转化为模仿信号,本体系即选用此种办法。

在单站无源定位技能中,常用的观测参数有方向角、抵达时间、频率、频率改变率、相位差改变率等。本文介绍的以4片D/A为根底的4通道信号模仿器,首要模仿的是多元天线阵列所接纳信号的相位差改变率。

1 原理剖析

本文所用D/A为双输入端口,每个端口最高速率为1.25 GSample·s-1,DDR形式,FPGA选用一般I/O口传输方法无法直接输出如此高速率的数据,则需经过多通道组成的并串转化技能来完成。本计划中FPGA输出端口作业在双路端口速率为800 Mbit·s-1,选用8通道数据组成1通道的方法为4片D/A芯片供应数字波形数据,故FPGA需发生共32通道数据。D/A作业时钟为1.667 GSample·s-1。

为组成宽带线性调频信号,假定其带宽为B,开始频率为f0,依据文献的推导,对每个组成D/A芯片所需的波形数据8通道数据,第j个通道的初相和第i个采样点的数据和频率步进码别离为

其间,f1代表D/A的作业时钟频率;f2代表每个通道的作业时钟频率;j代表通道号;i是终究信号的第i个采样时间的数据,则

。依据式(1)和式(2)的计算结果,可由FPGA发生4组8个通道的信号数据,经过并串转化输出给D/A,由此可得到所需信号的基准信号。

在文中,相位差的特定联系即空中渠道飞翔进程中天线阵列中的天线接纳到同一辐射源的相位改变联系,具体算法如下:本文模仿的天线阵列是四元阵十字天线阵列,天线平面与空中渠道飞翔轨道成30°倾角,由空中渠道的飞翔轨道与方针辐射源的坐标可得天线平面中心点与方针辐射源每一个时间的俯仰角和方位角,从而可计算出方针辐射源宣布的信号抵达天线阵列中每个天线的时延τk,将时延τk转化成相位差加入到FPGA发生的基准信号中,即可得到相位差实时改变且4路相位差之间有特定联系的4个通道信号。

2 硬件完成

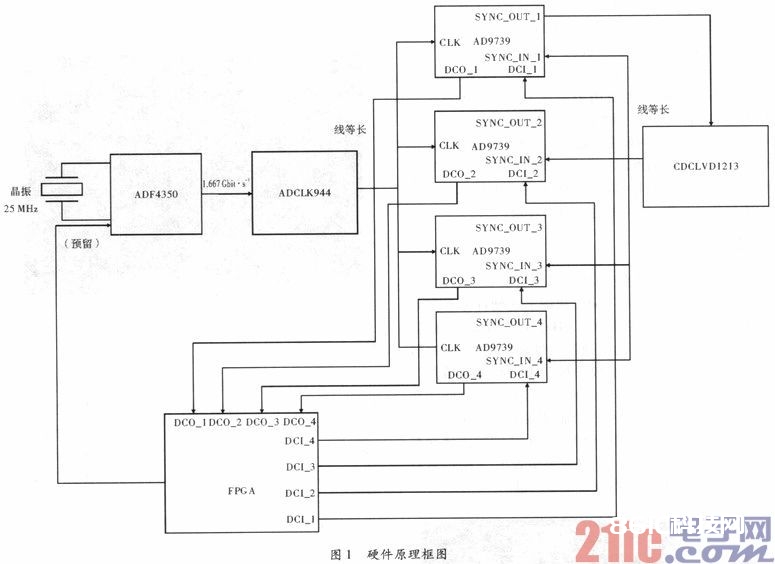

硬件渠道首要包括Xilinx公司的VIRTEX-5系列FPGA XC5VLX30;4片AD公司的2.5 GPS D/A转化器AD9739;AD公司的时钟倍频芯片ADF43 50;AD公司的时钟Buffer芯片ADCLK944;TI公司的时钟Buffer芯片CDCLVD1213及稳压电源芯片等,其硬件原理框图如图1所示。

XC5VLX30 FPGA是Xilinx公司依据65 nm铜工艺技能的新一代FPGA,包括32个DSP 48E Slice,最大400个用户可定义I/O以及最大1152个Block RAM,有6个时钟办理模块(CMT),每个CMT包括有2个DCM和一个PLL。

AD9739是AD公司推出的一款高速、高功用的RF数模转化器,双通道14 bit LVDS数据输入,内部采样频率可高达2.5 GSample·s-1,当作业在混合形式(MIX MODE)下,可将奈奎斯特二区或三区的输出信号用作发射信号,以削减混频环节。

ADF4350时钟倍频芯片内部NCO可将输入时钟倍频到2.2~4.4 GHz,然后经分频得到所需的时钟,体系选用1.6 GHz的时钟信号。

ADCLK944时钟Buffer芯片可输入恣意电平的时钟,然后悉数转化为LVPECL电平的时钟输出。CDCLVD1213时钟Buffer则可输入LVDS、LVPE CL或CML。

3 信号同步

在多通道信号模仿器的规划中,各通道之间的信号同步是重要的一环,在本体系中便是多片D/A之间的同步。

为完成这一意图,首先在硬件规划方面要做到如下等长:时钟Buffer ADCLK944供应4片AD9739时钟的线路需做到等长;FPGA与AD9379之间的时钟同步引脚DCO与DCI需别离等长;时钟Buffer CDCLVD1213供应AD9739的同步时钟线路需等长;FPGA与4片AD9739的数据输入线路需悉数等长。

其次,在DA装备上,输出同步信号(SYNC_OUT)的AD9739要装备成主形式(Master Mode),其他的AD9739均装备成从形式(Slave Mode)。

终究,FPGA进行相位补偿,如图1所示,一般情况下FPGA数据发生运用的是主片AD9739输出的DCO时钟,若经过以上两步,4片AD9739的输出仍不同步,FPGA则可替换用其他从片AD9739输出的DCO时钟发生数据。若此刻同步仍不抱负,就需求在FPGA程序中进行人工补偿,即人为地在同步欠安的某一路中增加相位推迟,使其能到达同步作用。

4 测验数据

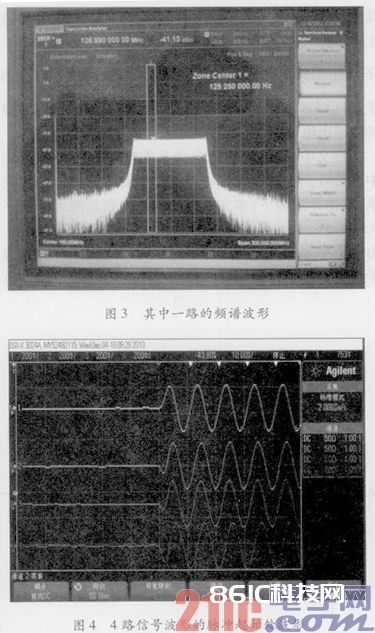

选用时钟芯片供应AD9739 1.6 GHz的作业时钟,AD9739作业于Normal Mode,运用上述硬件渠道完成初始频率100 MHz,带宽100 MHz,脉宽10 μs,各路信号间有必定相位联系的4通道线性调频信号,其时域波形如图2所示,用频谱仪剖析其间一路的频域波形如图3所示。本文终究发生的4路信号波形之间的相位差是一个改变进程,限于篇幅,无法将其改变进程具体展示,取其间间某组脉冲信号将4路信号的脉冲开始处打开,如图4所示。能够直观地看出,4路信号对齐的作用杰出,相位差存在且较为显着。

5 结束语

将FPGA与多片高速D/A AD9739结合,经信号同步,经过DDS发生中心频率在0~800 MHz之间,调频带宽600 MHz以内且4路有必定相位联系的线性调频信号,此计划在某空中渠道定位验证体系中作为测验辐射源。经验证,此体系能杰出地模仿多元天线阵列所接纳到的信号,一起定位体系可依据模仿器的输出信号定位出方针辐射源的方位参数。

本文多路信号之间只要相位信息不同,经扩展后,亦可发生多路之间频率、起伏、频率改变率等参数不同的多路宽带线性调频信号,即在FPGA中运用DDS发生多路信号时运用不同的初始参数。受限于D/A的作业频率,输出的信号频率较低。硬件布线未严厉等长以及元器材的误差使4路同步信号的时间差在ns级以上,关于某些需求准确定位的体系并不适用。怎么进一步进步多通道之间的同步性,依然是探究研讨的重要课题。