SOPC(System On a Programmable Chip,可编程芯片体系)便是在一个可编程芯片上完成一个电子体系的技能。SOPC是可编程逻辑器材技能和SoC(System on Chip)技能发展与交融的产品[1?2]。

SOPC的关键技能之一便是IP核,也便是知识产权核。所谓的IP核便是指将一些比较杂乱的功用模块,如音频编/解码、SDRAM等,规划成能够修正参数的模块,能够直接调用。实践的SOPC规划进程,用户常常有特别的需求,而EDA厂商未供给该IP核。所以,在规划中增加用户自界说组件显得特别重要。

1 Avalon总线

SOPC组件经过Avalon交流架构或许Avalon总线衔接在一起,SOPC体系的可定制特性要求Avalon总线也具有灵敏的可定制特性。Avalon总线是一种协议较为简略的同步总线,有其标准及传输形式。

Avalon总线是由Altera公司开发的一种专用的用于衔接SOPC体系组件及从组件的内部连线技能,它是由SOPC Builder主动生成,是一种抱负的用于体系处理器和外设之间的内连总线。一般运用的是Avalon从端口。一个典型从端口包括的信号如表1所列。

表1 Avalon从端口信号

Avalon总线运用很少的逻辑资源支撑数据总线复用、地址译码、发生等候周期和高档交流式总线传输。该总线为用户供给十分友爱的接口,屏蔽树立体系的细节,减轻了体系树立的工作量。

2 SHT11自界说IP核的开发

2.1 SHT11温湿度传感器

SHT11是瑞士Sensirion公司推出的SHTxx系列数字温湿度传感器。它是依据先进的CMOSens数字传感技能,具有极高的可靠性和长时刻稳定性。全量程标定,两线数字接口,大大缩短研制时刻,简化外围电路并下降费用。此外,具有体积小、呼应敏捷、能耗低、可浸没、抗干扰才能强、温湿一体的特色,兼有露点丈量,性价比高,使该产品能够适于多种场合的运用。SHT11的高档功用是经过状况寄存器来完成的[3]。

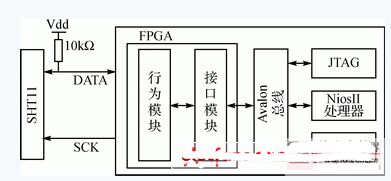

图1为体系结构图。由图可知,体系首要分为接口模块和行为模块,行为模块完成芯片的驱动逻辑功用,接口模块经过内部总线和Avalon总线相连,完成了对行为模块的操控。运用SOPC Builder树立体系,经过数据线和时钟线来操控SHT11。其间要加上10 kΩ的上拉电阻。

图1 体系结构图

选用自界说IP核的办法,也便是把SHT11当作外部存储器或许是I/O设备,将其作为从设备衔接到Nios II嵌入式处理器的Avalon总线上,体系用拜访I/O设备或许是读写寄存器的办法对其进行操控。所以,编写自界说IP核的时分,依据实体SHT11的时序要求,编写驱动、接口等,灵敏地操控并完成杂乱的时序。其间能够依照自己的需求灵敏地界说状况、标志位、操控位等。规划完成后,独立增加到SOPC Builder,用户能够直接运用。该办法比单纯运用PIO内核愈加节约处理器的开支,充分发挥了处理器的才能[4?6]。

2.2 接口模块的规划

依据SHT11的描绘,承认该模块与Avalon所需求的接口信号。经过运用较少的信号来处理读写。体系经过时钟线、数据线和SHT11相连,依据时钟的时序向数据线写指令,SHT11经过数据线输出数据。规划模块的输入信号为:clk,sysclk, n_rest, data_i,data_o,wr,rd, addr。输出信号为:SCK,DATA(DATA是双向数据线)。端口信号的部分阐明如下:

moduleSHT11(

clk,//体系时钟

n_rest,//体系复位

data_i,//Avalon写数据总线

data_o,//Avalon读数据总线

wr,//Avalon写恳求

rd,//Avalon读恳求

sysclk,//体系时钟

addr,//Avalon地址总线

SCK,//时钟线输出

DATA,//数据输入输出(双向)

);

2.3 行为模块的完成

行为模块完成的是SHT11的功用。该部分是整个规划的中心,完成对SHT11的操控。规划时有必要依据驱动操控的标准以及时序的要求来编写。规划的进程中,信号的操控较为杂乱,但在时序逻辑中,这又十分重要。能够设定一系列的寄存器,作为拜访硬件的通道[7?8]。

依据其驱动标准,不同的指令完成相应的功用。传输开端时,应该宣布发动信号。发动信号包括时钟线为高,数据线由高变低,并在下一个时钟线为高的时分将数据线变高。当发动信号开端后,输入相应指令(包括3位地址和5位指令),经过数据线,承认接纳到ACK信号后,表明SHT11现已正确接纳指令。待必定的时刻后,当数据线由高拉低后开端信号的传输。体系经过承认数据线上的ACK来承认每个字节的传输。数据传输结束,进行CRC校验。校验结束后,ACK为高,结束传输。

在进行规划时,选用嵌套状况机来完成驱动逻辑。依据驱动操控器的读写指令及读写时序,采纳不同状况机来完成,如图2所示。输入指令之后,依据不同的读写恳求,进入不同的状况机。

图2 状况机

经过rd和wr以及地址addr操控数据线的读写。当addr=1wr,则向数据线写数据(data_i),data_i 的输入格局是crc(1位)wr_data(16位)command(2位),当addr=0wr,进入状况机;当addr=2 amp; amp;rd,从数据线读取数据data_o。

设内部寄存器command,依据不同的指令,进入不同的状况机循环:若command为01,经过数据线向寄存器写数据;若command为 10,经过数据线从寄存器读数据;若command为其他,则读取数据。当传送8位数据后,需判别双向数据线DATA的ACK信号的凹凸,当接纳到ACK 信号时,再依据相应的指令,进行数据的传输。当数据传输结束后,需求经行CRC校验。图3是仿真时序图,完成向寄存器写数据的功用。

2.4 软件规划

该部分能够直接在SOPC Builder 中增加规划好的IP核和Verilog HDL 言语描绘的文件,并依据Avalon 总线传输标准设置好相关的信号线,如图4所示。这儿要注意,运用的是从端口。完成后,将IP核增加至SOPC中,树立内嵌体系,并编译下载到FPGA 器材中。