进步功用、增加功用、进步功率、下降功耗

一切 Virtex™-5 器材内的 550 MHz DSP48E Slice 能够加快算法,而且同上一代 Virtex 器材比较其 DSP 集成度更高、功耗也更低。

为您的体系有用增加强壮的、根据 FPGA 的 DSP 功用:

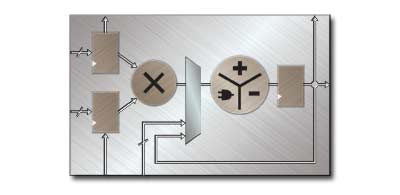

- 支撑 40 多种动态控制的运算形式,包含:乘法器、乘累加、乘加器/乘减器、3 输入加法器、桶形移位器、多种总线多路复用器、多种计数器和比较器。

- 高效加法链架构,能够有用完成高功用滤波器和杂乱算术运算。

- 低功耗要求:每个 DSP48E Slice 在 38% 的翻转率下功耗仅为 1.38 mW/100 MHz,比上一代 Slice 下降了 40%。

| 表1:Virtex-5 FPGA DSP48E 的特色和长处 | |

|---|---|

| 特色 | 长处 |

| 25 x 18 位二进制补码乘法器可发生 48 位全精度成果 |

在更大的动态范围内完成了更高的精度,能够以较少的逻辑资源(Slice 数)完成单精度浮点运算和多种滤波器。 |

| 增强型二级功用 |

运用带寄存器的累加反应功用(可选),完成了 3 输入、灵敏的 48 位加法器/减法器。 规划了形式监测器,支撑用于饱满算法的收敛性(无偏)舍入、下溢/上溢检测;以及主动复位计数器/累加器。 支撑单指令多数据(SIMD)功用 |

| 40 多种用户控制器操作形式 | DSPE Slice 在时钟周期改动时能够调整功用 |

| 18 位 B 输入级联布线 | 支撑输入采样传输 |

| 新式 30 位 A 输入级联布线 | 支撑先进的滤波器规划,并下降了功耗 |

| 独立的 48 位 C 输入 | 乘法、加法、大型三操作数加法、或灵敏的舍入形式。在整个 Slice 上消除了 C 输入同享,然后进步了利用率、简化了规划、进步了功用。 |

| 级联的 48 位 P 总线 | 支撑部分成果的输出传输。 |