跟着现代信息处理体系逐步向数字化、智能化和宽带化的方向开展,ADC体系成为了很多研讨范畴的瓶颈,怎么在有用地进步体系采样率的一起坚持较高的采样精度成为亟需处理的问题。除了经过工艺、电路结构等方面的改善设法进步单块ADC的转化速度外,经过时刻替换采样技能也是进步转化速度的一种有用办法。时刻替换采样选用多片ADC对同一模仿输入信号进行并行替换采样,然后能够成倍地进步整个ADC体系的采样率,一起整个采样体系的采样精度可根本坚持不变。

本文规划了一个用两片AD9480组成的时刻替换ADC体系,电路首要包含前置扩大、采样时钟信号发生、根据FPGA的数据收集操控与存储等几部分。时刻替换ADC体系完结时的首要问题是因为每片ADC之间功能的不匹配,会不可避免地引进通道失配差错,这些差错的存在会导致采样数据中呈现杂波重量,严重影响体系功能。为此文章评论了差错校对计划,针对三种首要的通道适配差错即偏置差错、增益差错及采样时刻差错,给出了校对计划,并在Matlab中对收集到的数据进行了验证,结果表明经过校对,通道差错能得到较好的消除。

1 时刻替换采样体系

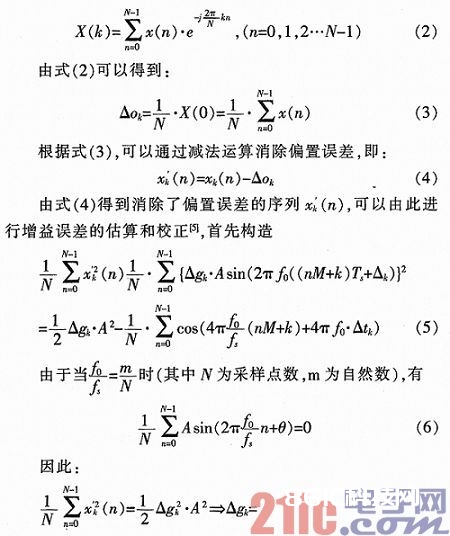

时刻替换采样体系的原理如下图1所示,使用M片采样率为fs/M的ADC以一个固定的时刻距离顺次对同一个输入模仿信号进行并行替换采样,相邻ADC之间的采样时刻距离为Ts=1/fs相位之间固定相差360/M度,如下图2所示。最终,将每片ADC采样数据拼接成一个总的采样数据输出。经过以上的操作,整个采样体系的采样率能够到达fs,进步为单

片ADC采样率的M倍。

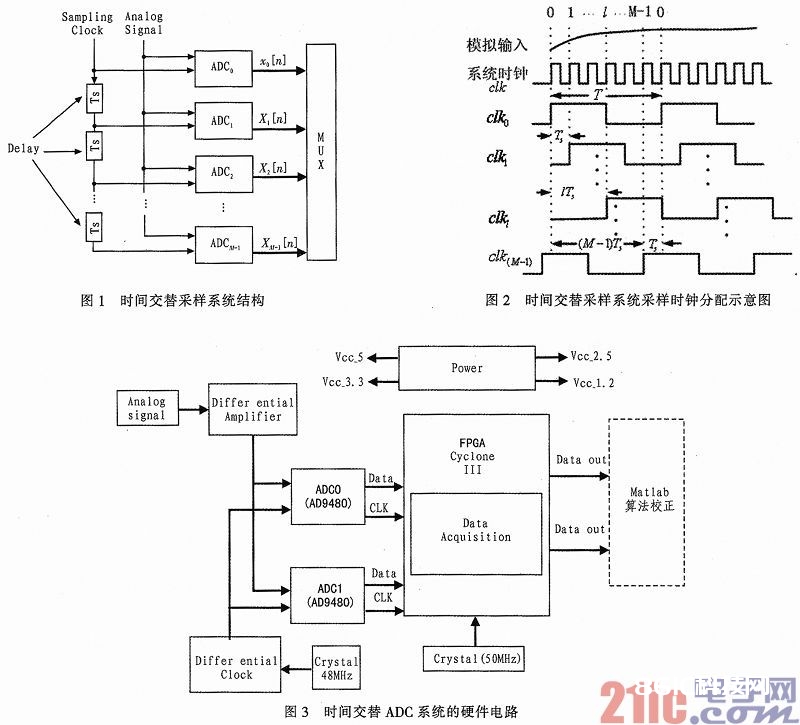

本文规划的体系选用两片采样精度为8bit,最高采样频率为250MSPS的AD9480芯片。整个硬件电路的组成如下图3所示,首要包含差分扩大电路、采样时钟发生和分配电路、ADC采样电路、FPGA操控电路及电源办理。

1)差分扩大电路

前置差分扩大电路选用ADI公司出产的AD8351芯片作为差分扩大器,这款芯片具有低功耗、低失真、大宽带的特色;而且能够作为单端和差分改换不同增益比的差分输出,其增益最大能够调到26 dB。规划中单端模仿输入信号经过差分扩大电路后发生共模电平为1.9 V,电压摆幅为350 mV的模仿LVDS差分信号。

2)时钟发生和分配电路

时钟发生和分配的规划是时刻替换采样技能完结的要害。规划中选用ADI公司的AD9518—3时钟芯片,这款芯片自带锁相环PLL电路;输出信号为LVPECL类型高速差分信号,其最高频率为1.6GHz;一起该时钟芯片能够发生三对时刻替换时钟信号通道,通道之间的时钟偏斜在10 ps内,且输出的时钟本身颤动要小于225 fs,因而是一款非常抱负的时钟芯片。规划进程中使用其两对时钟通道发生起伏相同,相位相反的差分时钟信号。

3)ADC采样电路

ADC采样电路选用的是AD9480芯片进行规划,这款芯片最高采样率为250MSPS,转化输出数字信号为8位,常温下实践有用位数典型值能够到达7.6位,是一款非常优异的高功能模数转化器。在其输出端不只输出LVDS采样数据,一起直接将输入的差分时钟做简略处理后也送到了输出端,便利后期对采样数据的处理。关于LVDS电平在高速电路PCB规划中,进行了特别的“蛇形”走线方法,以减小信号的反射串扰,一起在差分信号的接纳端接入100欧姆的电阻以完结阻抗匹配。

4)根据FPGA的体系操控

采样体系使用FPGA进行时钟芯片AD9518—3的寄存器装备以及对采样数据进行缓存和实时观测,这儿选用ALTERA公司Cyclone III系列的EP3C25Q240C8芯片作为操控单元,这款芯片是一款高性价比的FPGA芯片,作业电压为1.2 V,内部集成了24 624个逻辑单元;一起在芯片内部有多达66个M9K存储单元,能够被便利的装备成RAM、ROM、FIFO等,因而很容易地完结数据存储;别的芯片具有多达149个的I/O引脚,内嵌了4个锁相环(PLL),能够满意规划要求。

选用FPGA对整个体系操控的进程如下:FPGA上电复位后,对时钟芯片AD9518—3写入操控字以便完结时钟芯片的寄存器装备,这儿的装备进程即时钟芯片发生两路采样时钟的进程,经过装备后,发生两路巨细相同,相位相反的差分LVPECL时钟信号;一起采样时钟接入到ADC采样电路以操控采样进程,经过ADC采样通道后的采样数据和采样时钟一起经过异步FIFO处理,完结跨时钟域的数据传递,选取的FIFO深度为256,并将数据缓存到FPGA中,并经过QuaitusII软件中内部嵌入式逻辑剖析(SignalTap)实时观测FPGA引脚的采样数据,判别采样进程是否抱负,关于不抱负的数据需求从头进行采样;FPGA缓存的数据可进一步送到上位机中进行差错剖析和校对。

2 通道差错的校对

关于抱负的时刻替换采样体系,第k路采样通道的输出信号表达式为:xk(n)=x(nMTs+kTs),其间k=0,1,2,…M-1,n为采样点。然而在实践工程使用中,因为不同通道的ADC的采样特性不可能做到完全相同,会不可避免地发生通道失配差错,即偏置差错、增益差错及采样时刻差错。三种通道失配差错的存在,将会大大下降体系的功能。设第k路采样通道的偏置差错为△ok,增益差错为△gk,时刻差错为△tk,则实践采样进程中输出信号表达式为:

xk(n)=△gk·x(nMTs+kTs+△tk)+Aok,k=0,1,2,…N-1 (1)

关于频率为f0的输入信号,这3种差错在频域中的表现为:信号的频谱点在ω0(ω0=2πf0)处,偏置噪声的频谱点在k·ωs/M(k=0,1,2,…M-1);增益差错和时刻差错的频谱点在±ω0+(ωs/M)k(k=0,1,2,…M-1)。当采样体系的输入频率和采样通道数确认后这3种差错在频域中对应的频谱点都是确认,据此能够进行有用的预算和校对。

这儿通道差错预算进程以第一个采样通道作为参阅,假定该通道不存在增益差错和时刻差错,即△Ag0=1,△t0=0。设信号的采样序列为x(n),(n=1,2…N-1),则能够得到序列x(n)的DFT改换为: