保证多重FPGA电轨依正确次序封闭,跟保证开机程序是否正确相同重要,可防止设备因电压状况无法判别而提前毛病。

电源定序防止损坏

在发动现在的大型体系单晶片FPGA的多重电轨时,有许多技巧可用来操控其发动次序和时序。遵循设备制造商所指定的正确次序甚为重要,如此可防止设备抽取过多电流而导致损坏。

有些办法是透过操作各转换器的电源杰出输出,来操控次序中下一个供给的Enable脚位。如需求继电器,可刺进电容器。另一品种似的办法则是运用重置IC,在前一个供电到达所要的电压后发动下一个转换器。每种办法都有一些缺陷,且这些办法都无法操控电源封闭的次序。依正确的相反次序封闭电轨,跟敞开电源次序是否正确相同重要,都是为了保证设备能安全运作。

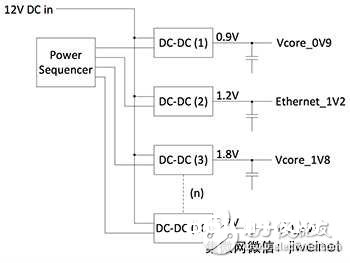

运用专用的电源定序IC,则更能安稳保证其次序正确。IC可程式化,在所要的时刻点别离传送Enable信号。图1显现多通道定序器怎么办理FPGA中心逻辑、周边和I/O电域。即使如此,电源封闭次序依旧难以操控,由于每个电轨上的去耦合电容器在转换器封闭后仍或许残留电荷,且残留时刻不一定,而每个电轨最多或许衔接多达20mF的总去耦合电容。

图1 透过定序IC办理FPGA电轨。

定序器坚持电源封闭操控

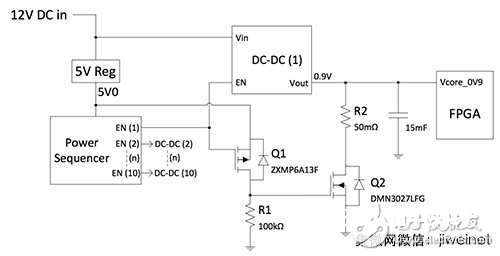

运用具有已知时刻常数的电路,自动将去耦合电容器放电,定序器便能坚持正确的电源封闭次序,其做法是在串联的电容器中暂时刺进放电电阻器。图2显现怎么在参加最少必要元件下,运用一对仔细挑选的MOSFET将电阻器刺进电路中。

图2 操控电源定序的自动放电电路。

电源定序器的EN输出衔接到DC-DC稳压器的Enable脚位,也衔接到P通道MOSFET(Q1)的闸极。定序器输出下降停用DC-DC稳压器时,Q1便会回转信号,敞开N通道MOSFET Q2。敞开时,Q2会透过R2电阻使15mF去耦合电容器放电到接地。

图中的电路假定DC-DC稳压器在供给关机信号后无法继续发生输出。假定DC-DC稳压器的输出能在收到关机指令后继续供给电源,则需求额定的继电器才干发动放电电路。

挑选的R2值有必要能保证恰当的放电时刻,让定序器能在可接受的时刻距离内完结关机。别的还要留意的是,电阻有必要够大,才干防止电流尖峰值上升率过快,防止引发EMI问题,以及对Q2和去耦合电容器组形成瞬态热应力。实务上,挑选R2值时需考虑一些额定的重要参数,像是Q2的导通电阻(RDS(ON))和电容器组的等效串联电阻(ESR)。

挑选MOSFET Q1时应参阅电源定序器的输出电压阈值。所选的设备应有够高的闸极阈值电压(VGS(th)),保证定序器输出为高电位时能坚持封闭,但要留意的是,VGS(th)会随接面温度上升而下降。本典范中挑选的定序器操作供给电压为5V,最小指定高电位输出电压为4.19V。Q1的VGS(th)在60℃环境操作温度下有必要大于0.9V,以保证运作正常。此外,闸极应运用100kΩ电阻下拉至源极电位,以防止误开。检查MOSFET材料表中VGS(th)与温度的标准化曲线,显现Diodes公司的ZXMP6A13F符合要求:保证最小VGS(th)在室温下为1V,到60℃则下降至0.9V左右。

在此典范中,咱们假定定序器有必要在100ms内封闭一共10V的电轨。因而,每个电轨的去耦合电容器组有必要在10ms内完结放电。方针是达到RC时刻常数8ms的3倍,保证电容器在要求时刻内放电到全电压的5%以下。核算RC常数时,电容器组的MOSFET RDS(ON)、寄生线路电阻和ESR都有必要与电阻器R2一起归入考量。

假定电容器ESR和线路电阻加起来不超越10mΩ,去耦合电容器组的总电容值为15mF,则RDS(ON)和R2的恰当值可用下列运算式求得:

3x(10mΩ+R2+(1.5&TImes;RDS(ON)))&TImes;15mF=8ms

假定R2=50mΩ,功率MOSFET Q2的RDS(ON)在VGS=4.5V且环境温度为25℃下有必要小于80mΩ。

挑选MOSFET时,温度相关改变的效应和RDS(ON)的批量变异也应考量在内。RDS(ON)在4.5V闸极驱动下、超出预期作业温度规模时的变异或许高达15mΩ。因而最好的做法是,确认R2为所选MOSFET之制造商指定最大RDS(ON)的两倍左右。假如R2为50mΩ,则可选用Diodes公司的DMN3027LFG N通道MOSFET。此设备在VGS=4.5V、室温下的RDS(ON)典型值和最大值别离为22mΩ和26.5mΩ。因而,RDS(ON)改变可从15mΩ到40mΩ,放电时刻从95%(3倍RC)的3.9ms起跳,运用最差20mF巨细的电容器组时放电时刻则或许拉长到5.4ms。

评价最大单一脉冲维护MOSFET安全