在程序中,需求延时的时分,一般情况下有两种办法:1、循环句子完结,这种办法简略易用,可是无法得到一个准确的延时时刻;2、守时器守时,可抵达准确延时。

中止的概念

什么是中止:CPU在处理某一事情A时,发生的别的某一事情B恳求CPU去处理(发生了中止),随后CPU暂时中止当时正在履行的使命,去对事情B进行处理,CPU处理完事情B后再回来之前中止的方位继续履行本来的事情A,这一进程总称为中止。

中止流程示意图

使CPU中止的事情称中止源。中止源向CPU宣布中止恳求,CPU暂时中止本来履行的事情A转去做事情B。事情B处理完毕后继续回来原先中止的当地(该进程称中止回来,原先中止的当地为断点),继续履行原先的事情。

中止的优先级

中止的优点

(1):进步了CPU的功率

CPU是核算机的指挥中心,它与外围设备(如:按键,显示器等)通讯的办法有查询和中止2种

2:中止:在外围设备需求通讯服务时主动告知CPU,CPU停下当时作业去处理中止程序,然后进步了CPU的作业功率。

(2):能够完结实时处理

外设任何时分都或许宣布恳求中止的信号,CPU接到恳求后及时处理,以满意实时体系的需求

(3):能够及时处理毛病

核算机体系运转进程中难免会呈现毛病,eg:电源中止,存储器犯错,外围设备作业不正常等,这时能够经过中止体系向中止源的CPU宣布恳求,以便处理毛病。

守时器的运用过程

1.翻开总中止:

EA(ENABLE ALL) = 1;

2.设置守时器作业方法:

TMOD寄存器:守时器/计数器形式操控寄存器

其间M1和M0是守时器作业方法的设置位,共可设置4种作业方法。

方法0(M1M0 = 00):13位守时/计数器

方法1(M1M0 = 01):16位守时/计数器 //一般选用方法1

方法2(M1M0 = 10):8位主动重装守时/计数器

方法3(M1M0 = 11):T0分为两个独立的8为守时/计数器;T1在此方法中止计数

3.守时器填装初值

填装初值关键:

①单片机晶振频率:12M,震动周期为1/12us

②规范的51单片机为12T,即12个时钟周期, 12 x 1/12 us = 1us,即加一次1us。

例如:将守时器设置在作业方法1,初值设为10ms:

TMOD = 0x01;

TH0 = (65536 – 10000);//10000代表10000个1us

TL0 = (65536 – 10000);

4.翻开守时器中止

ET0 = 1:ENABLE TIME0

ET1 = 1: ENABLE TIME1

5.翻开守时器(开端计数)

TR0 = 1:翻开守时器0

TR1 = 1:翻开守时器1

6.写中止服务函数(ISR)

留意:中止服务函数不能有参数和回来值

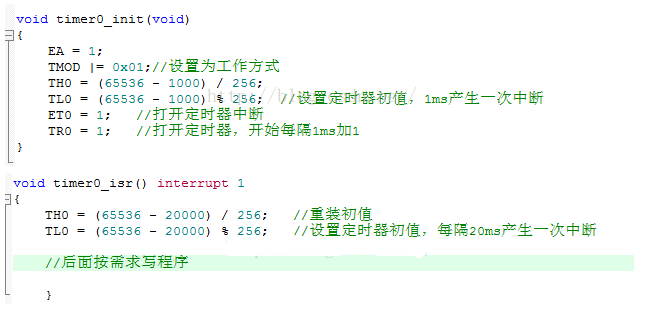

守时器运用程序

留意:

1:守时器和中止都归于单片机的内部资源,在开发板上是没有芯片的,一起守时器的初始化程序一旦溢出,会主动去履行守时器中止子程序,而不需求咱们自己去调用,这些都是由硬件直接操控的。

2:守时器核算的是固定脉冲,其守时时刻是能够核算出来的。它比延时函数有更好的效果,能进步CPU 的功率,由于延时函数是需求消耗CPU去履行的,在此期间,CPU是不能履行其它功用的,而守时器是需求用到 的时分,CPU主动调用。

s3c2440的守时器运用办法

体系时钟

首要,应先了解s3c2440的时钟体系。MCU的主时钟源主要是外部晶振或外部时钟,现在用的最多的是外部晶振。MINI2440开发板运用一个12MHz的外部晶振,假如CPU只作业在12MHz频率下,开发板的运用功率十分低,一切依靠体系时钟作业的硬件,其作业功率也十分低,假如想进步CPU的作业功率,则需求对输入时钟进行一系列处理,其流程如下:

晶振频率经过PLL(锁相环)进行倍频处理。s3c2440有两个PLL,别离是UPLL和MPLL。UPLL专用于USB模块,供给48MHz,MPLL供给FCLK、HCLK和PCLK。FCLK是主频时钟,用于ARM920T内核;HCLK用于AHB总线设备,如内存操控、中止操控、LCD操控、DMA以及USB主模块;PCLK用于APB总线设备,如外围设备的看门狗,IIS,I2C,PWM,MMC接口,ADC,UART,GPIO,RTC以及SPI。

s3c2440支撑FCLK、HCLK和PCLK之间的分频份额挑选,该份额由CLKDIVN寄存器中的HDIVN和PDIVN来决议。因而,咱们只需确认FCLK,即可经过设定HDIVN和PDIVN来确认HCLK和PCLK。

FCLK与输入时钟Fin之间的倍数联系(即晶振频率经过PLL倍频)是经过MPLLCON寄存器(如图1所示)来设置的,MPLLCON寄存器中包括3个参数:MDIV、PDIV、SDIV,公式如下:

MPLL(FCLK) = (2*m*Fin) / (p*2^s)

其间:m = MDIV + 8 , p = PDIV + 2 ,s = SDIV

图1 MPLLCON寄存器

总结一下,时钟发生流程为:外部时钟源→经过寄存器MPLLCON得到FCLK→再经过寄存器CLKDIVN得到HCLK和PCLK。

守时器

s3c2440有5个16-bit的守时器,守时器0、1、2、3具有PWM功用;守时器4只要一个内部守时而没有相关到输出管脚上;一起,守时器0有一个dead-zeno发生器,用于大电流设备。

守时器的输入时钟频率信号跟预分频器(prescaler)和分频器(divider)相关。如图2所示。

预分频器:守时器0和1同享一个8-bit预分频器,守时器2、3、4同享另一个8-bit预分频器,预分频器数值由TCFG0装备,取值规模是0~255。

分频器:一起,每一个守时器都别离有一个时钟分频器,这样就能够发生5个不同的分频信号,分频器数值由TCFG1装备,取值只能是2、4、8、16,或许外部TCLKn。

图2 守时器输入时钟框图

详细公式为:

守时器输入时钟频率=PCLK ÷ (prescaler+1) ÷ divider

比方,已知PCLK=50MHz,咱们期望某一个守时器的输入时钟频率为25KHz,那么咱们就需求装备prescaler=249,divider=8,则递减计数器每减一次1,时刻就过去0.04ms(1÷25000×1000)。

TCONn为守时器操控寄存器,操控守时器的敞开与封闭。

守时计数缓冲寄存器TCNTBn用于存储守时器的初始值,当守时器发动时,TCNTBn里的数值会被加载到递减计数器TCNTn中。

守时比较缓冲寄存器TCMPBn用于存储守时器的比较值,TCMPBn的数值会被加载到比较寄存器TCMPn里来跟递减计数器进行比较。

作业原理为:

(1)将守时器的初始值和比较值装入寄存器TCNTBn和TCMPBn中。

(2)设置守时器操控寄存器TCON,发动守时器。此刻,TCMPBn和TCNTBn中的值会加载到寄存器TCMPn和TCNTn中。

(3)守时器会减1计数,即TCNTn进行减1计数,当TCMPn=TCNTn时,TOUTn引脚输出取反。

在一般使用中,TCMPBn的值用于PWM,当递减计数器和比较计数器数值持平时,电平会翻转,然后抵达改动占空比的意图。假如仅仅是用于守时中止,那么将TCMPBn设置为0,则当递减计数器抵达0时,守时器中止恳求告诉CPU守时器操作现已完结。当守时器计数器抵达零时, 相应的 TCNTBn的值将主动被加载到递减计数器以继续下一次操作。可是,假如守时器中止了,例如,在守时器运转形式期间铲除TCONn的守时器使能位, TCNTBn的值将不会被从头加载到计数器中。

s3c2440的守时器有一个双缓冲功用,确保下次守时器操作时重加载的值改动时无需中止当时的守时器操作。所以新的守时器的值设定,当时的守时器操作也能够成功完结。守时器的值能够写到TCNTBn中,守时器的当时计数值能够从TCNTOn中读到。TCNTBn被读取的值,不标明计数器的当时状况,而是下一次守时器继续期间的重加载值。当TCNTn为0,主动重加载操作会仿制TCNTBn到TCNTn中。可是,假如TCNTn为0,而主动重加载的使能位为0,那么TCNTn不会再操作了。

装备完守时器相关内容,接下来是装备中止,如设置中止形式(IRQ或FIQ),将守时器履行函数对应守时中止进口地址等等,这儿不多加赘述。