1、 导言

Σ-Δ调制在数字信号处理以及通讯体系方面的运用正越来越引起咱们的注重,因为Σ-Δ调制完成时首要选用数字技能而且对模仿端的精度要求不高,Σ-Δ调制一般都是对模仿信号进行调制发生一位数字信号。但许多情况下,输入信号自身便是数字信号,这时就非常有必要研讨对数字信号的Σ-Δ调制完成方法。

在本文中,迁就数字Σ-Δ调制器的基本原理进行论述和研讨,然后对数字Σ-Δ调制器结构进行论述和规划,并终究FPGA完成,终究进行总结。

2、 Σ-Δ调制器的原理

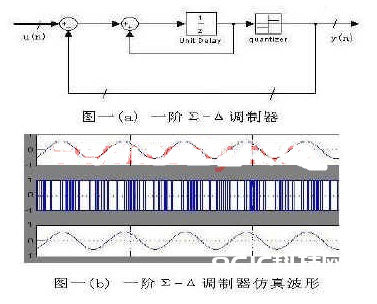

Σ-Δ调制器是一个非线性的体系,由一个滤波器,一个带反应回路的一比特量化器和一个减法器组成,其间量化器作业频率要远比奈奎斯特采样频率要高,整个体系原理图如图一所示,输入信号经调制后得到的比特流信号能够很好的恢复出信号。

信号与反应信号的差值在累加器(滤波器)中累加,然后由量化器量化。在此假定量化器引进的噪声为e(n),则,很简略得到y(n)和输入u(n)及噪声e(n)之间在Z域的联系,即:

![]()

由式(2.0)能够看出,一阶Σ-Δ体系对输入信号的传输函数STF为

![]()

它对信号发生一个单位的推迟,而关于噪声的传输函数NTF为

![]()

噪声传递函数在直流处有个零点,所以出现一阶高通滤波的性质,由此能够看出,噪声被推挤到较高频段,在信号带宽以内,量化噪声被大大削弱。

3、 数字Σ-Δ调制器的规划

图二显现的是一个一阶的数字Σ-Δ调制器的体系框图,这个Σ-Δ调制器对输入的8位信号进行调制。

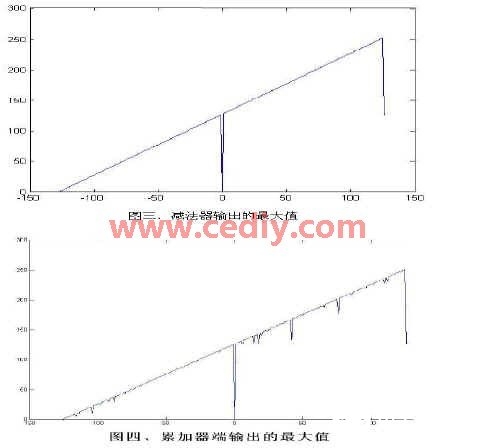

这个一阶数字Σ-Δ调制器中,减法器加法器和量化器都是对8位信号进行的运算,减法是两个8位信号的运算,所以有必要是一个九位的减法,这以后的加法器与推迟单元组成了一个累加器,对前面的减法电路得到的值进行累加,咱们对累加器端的输入进行估量,因为Σ-Δ调制器的特色,假如累加器前一个累加成果的是一个正信号,那么反应回输入端的是一个负值,反之,反应回输入端的是一个正值,这样,累加器的累加成果将一直在一个有限的规模内,所以,咱们能够估量,累加器的位数有可能将只需求9位。图三,图四所显现的仿真波形是减法器和加法器在Σ-Δ调制器对八位信号进行调制时的输出规模,横坐标表明的是输入规模,纵坐标表明的是在各种输入情况下输出的最大值。仿真成果证明了咱们的猜测。

从图三、图四能够看出,对八位信号调制时,减法器和累加器电路的输出的绝对值不会超越256,实践电路的信号都是补码表明,运算也都是补码运算,所以设计时只需求规划一个九位的减法器和一个九位的累加器就能够满意体系需求。

本体系规划中,各运算单元的操作数都是补码,最高位为符号位,所以量化器便是一个简略的挑选器,符号位为正得1,符号位为负得-1,反应回路中的转化器则是一个简略的数据挑选器,在此考虑到反应信号将做减法运算,所以在+1时挑选输出负值,在-1时挑选输出正值,这样,减法器就直接规划成一个加法器,这样能够简化规划。

4、 Σ-Δ调制器的FPGA完成

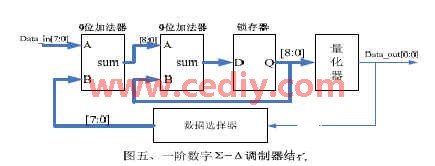

通过对图二的详细单元剖析,咱们能够得到一个如图五所示的详细的FPGA可完成的结构图。

这样一个数字一阶Σ-Δ调制器在FPGA完成的时分只需求两个9位的加法器,一个锁存器,一个简略量化器和一个数据挑选器,而且,量化器和数据挑选器都是极端简略的,所以在FPGA完成时只需消耗很少的逻辑资源。。本文选用Xilinx Spartan 3系列的XC3S200-PQ208完成。输入信号为8位宽的二进制数据Data_in[7:0],时钟信号为Clk,复位信号为Reset,输出信号为单比特信号Data_out[0:0]。

本规划运用verilogHDL言语描绘,通过xilinxISE6.i编译归纳,归纳东西运用xilinx XST。下面给出该模块的首要可归纳的verilogHDL描绘:

//一阶数字Σ-Δ调制器

module sdelta(data_in,clk,reset,data_out);

input [7:0] data_in; //输入信号

input [0:0] clk,reset;

output [0:0] data_out; //输出信号

reg [0:0] data_out;

reg [8:0] sum1; //减法器端的输出

reg [8:0] sum2; //累加器端的输出reg

reg [8:0] latch_out; //锁存器端的输出

reg [7:0] choose_out;//数据挑选器输出

always @(data_in or choose_out) sum1 = data_in + choose_out;

always @(sum1 or latch_out) sum2 = sum1 + latch_out;

always @(posedge clk or posedge reset)

begin

if(reset)

begin

data_out 《= 1‘b0;

latch_out 《= 9’b000000000;

choose_out 《=8‘b00000000;

end

else

begin

latch_out 《= sum2;

data_out 《= latch_out[8]?0:1;

choose_out《=latch_out[8]?8’b01111111:8‘b1000000;

end

end

endmodule

5、定论

本文咱们从Σ-Δ调制原理开端,逐渐给出了一阶数字Σ-Δ调制器的体系规划以及终究可完成的FPGA模型。Σ-Δ调制器能够很便利的运用在各种数字体系中,比方单比特神经网络权值调整,单比特运算单元信号的发生,由此能够大大的下降体系结构的复杂性,并大规模的削减电路单元之间的连线。在处理超采样频率发生的情况下,运用将是非常广泛的。

本文作者立异点:Σ-Δ调制器一般用于模数信号的转化,对多比特数据转化成单比特数据研讨比较少,本文给出了一种切实可行的数字Σ-Δ调制器结构和完成方法,而且因为对加法器做了必要的规模估量仿真,大大下降了体系所需占用资源,能够很便利的运用于各种需求确保精度的单比特数字信号处理场合下。

责任编辑:gt