1.导言

近年来,跟着电子技术的飞速发展,杂乱可编程逻辑器材(CPLD)得到了越来越广泛的运用。CPLD由一个“门”阵列和一个“或”阵列组成,恣意一个组合逻辑都能够用“与-或”表达式来描绘,因而能够运用CPLD完结各种数字逻辑功用。

本文依据便携式示波表的全体规划项目,针对怎么选用CPLD完结示波器峰峰值采样的快速显现,进步体系功率进行了探究和研讨。经过CPLD完结对液晶屏上同一列的多点显现是本规划的立异点。规划运用的CPLD足Altera公司出品的MAx IIEPM1270T144C5。

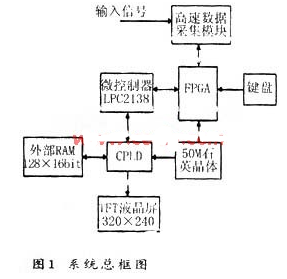

2.硬件总体规划

整个体系首要由高速数据收集模块,可编程逻辑器材FPGA,微操控器LPC2138,以及显现等四部分组成,体系框图1:

数据采样首要由高速模数转化芯片AD9480完结,实时采样率为250M,采样取得的数据存储在FPGA内部SRAM中。微操控器芯片选用嵌入式芯片LPC2138,首要担任对采样数掘的读取以及处理,然后传送到CPLD中。杂乱可编程逻辑器材CPLD,对LPC2138传送过来的数据进行处理,将数据写入对应的外部RAM地址中。RAM的地址空间为128K,而显现屏液晶点数为320×240=76800、即75 K。RAM的地址与液晶点的对应关系为1对1。显现进程为CPLD经过定制计数器发生累加地址,读取RAM中数据,按显现屏时钟频率,每个时钟脉冲传送一个数据到对应显现屏方位进行显现,时钟频率为6.25MHz。

3.同列多点显现

3.1 规划思路

以往常用的示波表液晶屏显现办法是,波形更新时,微操控器经过逐点操作的办法,将每个点将要在屏幕显现的方位经过向RAM发送地址和数据来写入,再由CPLD的显现模块读取RAM数据进行显现。可是,当一次需求批改的点数较多,尤其是处于示波表的峰峰值显现办法时,假如仍选用微操控器进行逐点批改的办法,由于LPC2138操控芯片的操作频串不够高,代码指令行过多,将大大下降显现的更新速度,导致波形改写率下降,不能将高速采样的成果当令呈现在屏幕上。因而,这儿运用CPLD可灵敏规划的特色,在峰峰值显现或许需求对同一列进行多点与操作时,只需经过LPC2138向CPLD发送该列的首地址和需写入点的个数,剩余的写操作悉数由CPLD得用时钟节拍来完结,大大进步了波形显现的改写速度。

3.2 显现节拍的组织

CPLD内部将体系时钟50MHz四分频,再四分频发生4个节拍,发生时钟节拍的框图如图2。

“CPLD读RAM时钟”由前3个节拍组成,是CPLD对RAM的读地址操作。 “显现时钟”由1、3节拍组成,等于液晶屏的显现频率,也等于CPLD的地址发生频率,由所以4个节拍里的2次不同的上升沿,所以频率为(50M/4/4)x2=6.25MHz.第4个节拍,是在写使能有用的情况下,将LPC2138发送的数据写入对应RAM地址。第2个节拍,便是咱们这儿用来进行同列多点批改时的时钟源。

3.3 同列多点显现模块规划

模块地址输入端的结构框图3所示。

ADD_IN[16..0]是微操控器发送过来的待写入RAM的列的首地址,EN是写使能操控信号地址作为锁存器的输入,锁仔器使能端由EN操控,当使能端有用时,锁存器输出端的“开端地址”等于ADD_IN[16..0]。在前面ADD IN[16..0]和EN还经过了一级D触发器来加强同步性,EN经过的D触发器有一个清零端,由READY信号操控,关于这个信号后边有具体阐明。

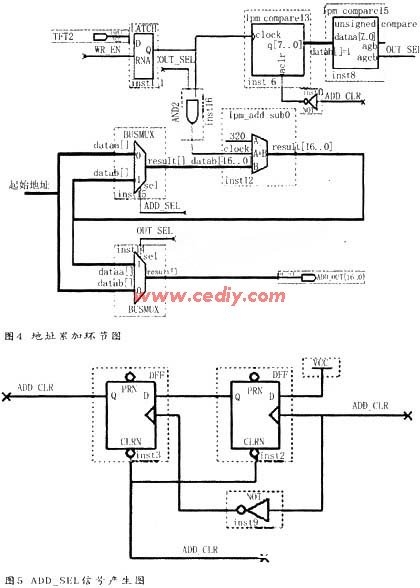

“开端地址”进入下面一级地址累加环节,用以发生同一列从上到下各点的地址,这是本规划的中心部分,其结构榧图如下:

“开端地址”进来后,遇到两个2选1的总线挑选器,上面一个挑选器的挑选端信号是ADD_SEL,它挑选进人累加环节的地址;下面一个挑选器的挑选端信号是OUT_SEL,它挑选输出的地址是原始地址仍是经过累加之后的地址。

地址累加的时钟源挑选的是上一末节所述4个节拍中的第2个,其实从原理逻辑上讲运用第3个节拍也能够,可是考虑到数据传输进程中的延时要素,为了在笫4个节拍曾经发生安稳有用的写地址,这儿仍是挑选第2个节拍作为时钟源。时钟源前面加了一级锁存器,其使能端信号是上一个框图所示的WR_EN,这个信号相当于一个开关,为1时,运转后边的同列多点地址批改操作,地址累加;为0时,中止地址累加,一向输出原始地址。

加法器的时钟是时钟源和OUT_SEL信号相与后的输出,当两者一起有用时,才会发生高电平,OUT_SEL的发生将在后边阐明。如图所示,计数器的时钟来自时钟源,当WR_EN有用时,计数器开端计数,计数器的位数这儿约束在8位。由于依据示波表上的波形有用显现区域,同一列最多只需求显现199个点,而8位二进制数规模从0~255,现已能够满意显现要求。假如需求显现的规模更大,只需更改计数器输出位数即可。

计数器的输出接到一个8位比较器的输入端dataa[7..0],与datab[7..0]=1比较。这儿设置与1比较是很重要的,当WR_EN有用时,模块开端作业,计数器时钟输入有用,第一个上升沿来到,计数器输出为0,经过比较器,0比1小, 因而ageb输出(a大于等于b)为0,即OUT_SEL为0,输出的第一个写地址为原始地址。第二个上升沿到来时,计数器输出为1,经过比较器,1等于1,则ageb输出OUT_SEL也为1,输出的第二个地址为累加一次之后的地址。以此类推,再往后的时钟沿一向使比较器输出OUT_SEL为1,输出的地址便是逐次累加后的地址。当一次同列多点写入完结后,有必要对计数器进行清零,以等候下一次操作到来,清零端信号为ADD_CLR经过非门之后的输入,ADD_CLR的发生将在后边描绘。

由此可见,第一个时钟上升沿来时,加法器的输入ADD CLK无效,只要第二个上升沿来时,ADD_SEL挑选原始地址作为加法器输入,加法器完结一次地址加320的操作,这儿将加数定制为320是由于显现屏标准为320×240,每—行320个点,同一列上下一个点与上一个点的地址相差便是320。从第三个上升沿开端,ADD_SEL会挑选批改后的地址作为加法器输入,以此完结地址累加。ADD_SEL信号发生的原理框图如下:

第二级D触发器的时钟是ADD_CLK经过非门的输出,这样做的成果是,在ADD_CLK的下降沿输出ADD_SEL等于1。结合上面的逻辑框图能够看出,第二_个时钟源上升沿到来时,即笫一个ADD_CLK上升沿,ADD_SEL为0,直到ADD_CLK的下降沿,ADD_SEL才变为1并一向坚持,以此完结了上面所述的加法器地址输入的挑选操控。

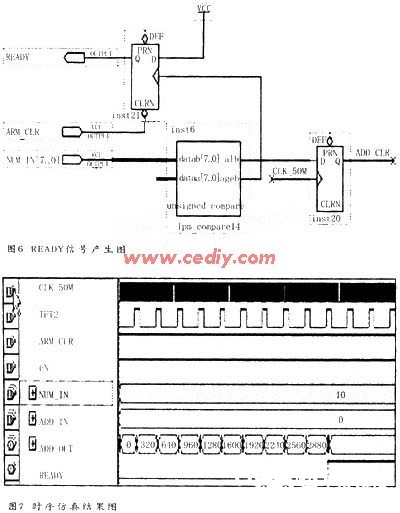

一次同列多点写入完结之后,会发生一个反应信号READY供LPC2138查询,查询到READY有用,才进行下一次操作,不然等候。其结构框图如下:

NUM_IN[7..0]是微操控器发送给CPLD的同列批改点个数的数据,连接到8位比较器的一个输入端datab[7..0],比较器另一输入端dataa[7..0]则为前面所述8位计数器的输出。当计数器的输出夫于等于NUM_IN[7..0]输入时,ageb端输出为1,发生一个上升沿,使READY变为1,一起a1b也输出发生一个上升沿,使ADD_CLR信号变为1,这个信号用来对计数器进行清零。READY信号除了供微操控器查询外,还有一个效果便是对WR_EN信号禁用,使整个模块中止作业,直到微操控器发送指令ARM_CLR铲除READY信号,模块才重新开端作业。

该模块的时序仿真成果如图所示,开端地址为0,列批改点个数为10,体系时钟50MHz,时钟源频率3.125MHz,占空比25%,ADD_OUT为模块输出地址:

前面均是关于同列多点批改的描绘,当需求进行单点写操作时,只需让输入NUM_IN[7..0]等于0即可。

4.软件操控

LPC 2138对模块的操控很便利,经过编写C言语代码,在发送地址和计数次数数据前,先查询READY信号,假如有用则铲除READY信号,并发送数据,之后又转入查询状况,以此循环。关于ARM_CLR信号,开端设计时专门由微操控器发送指令来发生,后为进步功率,直接用写使能信号(EN)发生,经测验可用。

5.结语

运用杂乱可编程逻辑器材(CPLD)来完结对等候显现的同列多点的RAM写入是可行的。经过屡次对计划的改善批改,现在的模块现已能够很安稳的作业,微操控器LPC2138对其的操控也简洁明了。假如需求进行同行多点的批改也能够选用这种规划计划,乃至将两者结合起来,经过一个操控端进行挑选。这儿由于首要运用在示波表峰值显现形式,故只选用同列多点批改的规划。

责任编辑:gt