在快节奏的现代社会,时刻变得越来越名贵。关于时钟的电子规划,高精度且低功耗逐步成为干流。笔者就有一个轿车显现屏的时钟显现项目,要求时钟一天的差错操控在1s以内。要想达到此要求,则有必要满意晶振的频率误差PPM<1/60/60/24*1000*1000=11.574ppm。世强团队清晰了如此的高要求后,引荐咱们选用EPSON的车载实时时钟RA8900CE,并全程为供给技术支撑服务,给咱们的研制缩减了不少时刻。

RA8900CE契合AEC-Q200认证规范,是一颗集成32.768KHz晶体单元的高精度DTCXO,全温度规模频率误差为5ppm,作业电流十分低,仅为0.7uA/3V(Typ.)。并且,RA8900CE支撑高达400KHz的IIC通讯,接口电压支撑2.5V~5.5V。最主要RA8900CE的封装仅为2.5mm*3.2mm,小封装有利于PCB走线,便利咱们把RA8900CE放置在MCU邻近,大大降低了PCB布线难度。因而,其既满意晶振要求又降低了PCB布线难度,可谓是一箭双雕。下面我环绕项目研制规划过程中的关于RA8900CE运用状况及问题处理做了具体介绍。

问题总揽

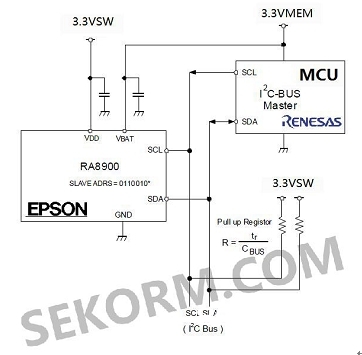

添加RA8900CE芯片后,咱们发现样品初度上电后,DAB芯片无法和MCU正常通讯。样品的电路框图如下图所示:

图1:轿车显现屏的时钟显现电路框图

问题剖析及处理

样品初度上电,DAB芯片无法和MCU正常通讯。这是个赋有应战的问题,为了探求原因,咱们选用排除法的考虑方法,剖析如下:

图2:问题剖析

首要,要确定导致问题的模块。咱们先承认DAB上电时序,如图3所示,DAB芯片对上电时序有要求,即接口电源DVDDIO必定要在主电源VBAT之后上电。可是,咱们测验后发现DVDDIO提早于VBAT上电,从而导致DAB通讯反常。导致DAB通讯反常的原因找到了,可是,终究为何上电时序会不满意?

咱们规划的DAB电源如图3所示,经过MCU操控5VSW和3.3VSW,确保5VSW提早与3.3VSW上电,理论规划彻底满意DAB上电时序要求。可是,为何实际状况和理论规划的状况相差甚远?

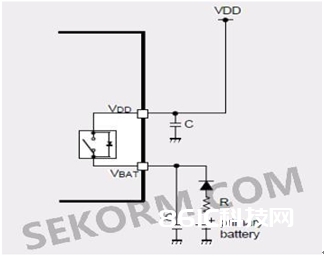

图3:DAB上电时序

经过丈量电源时序,终究咱们发现是因为追加的RA8900CE芯片,在初始上电阶段导致电源串电,3.3VSW电源跟从3.3VMEM提早上电,导致不契合DAB上电时序要求。RA8900CE的内部电路如图4所示,为了避免3.3VSW没电时,产生串电现象,咱们设置RA8900的寄存器地址为:VDETOFF,SWOFF=(1.1),这样设置是确保RA8900CE内部VDD和VBAT之间的开关永久坚持关断状况。可是机器第一次上电的时分,RA8900CE的寄存器为默认值,而咱们的软件只要在MCU起来后才能够设置RA8900CE的寄存器地址为:VDETOFF,SWOFF=(1.1)。这样,就会导致有一段时刻VBAT和VDD直连,导致3.3VSW电源跟从3.3VMEM提早上电,从而导致DAB和MCU通讯反常。

图4:RA8900CE的内部电路

知道了问题的底子原因,找到处理计划就变得很简单。因为RA8900CE作业时VDD电源耗费的最大电流是1.45uA,电流耗费十分小,因而咱们决议选用VDD和VBAT共用一个电源的计划,即都运用3.3VMEM电源。如此一来就底子的处理了串电问题,从而确保了DAB的上电时序,处理了DAB和MCU无法通讯的问题。

问题总结

简而言之,疏忽了RA8900CE的寄存器设置条件,导致初始上电时DAB上电时序反常,终究导致DAB无法通讯。尽管咱们处理了此问题,可是假如从规划源头开端就留意RA8900CE寄存器的设置条件,则会从底子上根绝此类问题的产生。电子规划容不得一点大意,常常差之毫厘谬以千里,期望我的阅历能给运用RA8900CE芯片的小伙伴们供给协助,防微杜渐,不要让相似的问题再次产生。

世强作为全球最大的晶体时钟产品供给商EPSON官方指定署理商,全线署理EPSON旗下的晶体、晶振、实时时钟等芯片,在轿车车身、底盘、动力体系、车载、ADAS、安全体系,以及新能源轿车上都能供给老练的处理计划、Demo支撑和技术服务等。

上述这样的文章世强元件电商渠道有十分多,咱们也欢迎有相似内容的研制工程师前往世强元件电商渠道投稿。被选用的稿件都有酬劳哦。