视频方针运动检测是从视频序列中提取出有意义的运动方针,它是视频检索、多媒体内容描绘以及根据内容的视频编码的根底。接连帧间差分法 、布景差分法和光流法是视频方针切割的常用办法。接连帧间差分法关于动态环境有很好的适应性,但不能彻底提取出视频方针的一切相关点;布景差分法能够较完整地提取方针点,却又对光照和外部条件形成的动态场景改变过于灵敏;光流法尽管能够直接用于摄像机运动下的视频方针检测,可是大多数光流办法的核算杂乱,不适于实时处理。将时域和空域信息进行有用的交融就能够得到更有用的成果,但还存在着方针概括检测的不完整性和方针相关点保存较少的问题。本文在运用FPGA采样得到视频图画的根底上,提出了一种对Pan办法改善的布景重建办法,进一步的提高了视频方针切割的作用。

1 硬件体系

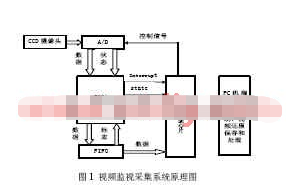

体系原理图

整个体系以FPGA和TUSB3210为中心,担任视频数据的接纳处理,发动A/D转化,操控FIFO的读写及采样频率的设定,与主机之间的通讯及数据传输。

A/D、FIFO和USB操控芯片

视频收集部分选用了Philips公司的视频A/D转化芯片SAA711A(EVIP),经过USB操控芯片供给的一对I2C引脚SDA和SCL进行操控;FIFO选用选用TI公司SN74V293芯片,它的容量为65536×18bit 或131072×9bit,最快读写周期为6ns,能够满意100MHz采样数据的存储。

SN74V293有独立的读写时钟操控电路,答应读写操作一起进行。SN74V293内部有满、空、半满输出信号以及可编程设定的简直满和简直空输出信号,经过这些信号操控器能够灵敏操控FIFO的读写操作。

USB操控芯片选用TI公司的TUSB3210,它是TI公司推出的内嵌8052内核并带有USB接口的微操控器芯片。TUSB3210有256字节的内部RAM,8K字节的程序RAM,512字节的USB数据缓冲和端点描绘块EDB(Endpoint Descriptor Blocks),4个通用的GPIO端口P0、P1、P2、P3,I2C接口电路,看门狗电路等。当主机与芯片进行USB通讯时,会发生外部中止0,经过中止矢量寄存器判别。经过界说Setup_packed_Int、Input_endpoint0_Int、Output_endpoint0_Int这三个中止,用于与主机树立衔接、进行操控传输或中止传输;Input_endpoint1_Int、Output_endpoint1_Int这两个中止首要在批量传输时运用。而在固件中别离履行不同的中止程序来完结USB的数据传输。

FPGA操控的完结

FPGA选用XINLINX公司的XC3142,PC终端经过USB口向视频收集卡传送start信号,告诉视频收集卡开端作业。视频信号经过CCD摄像头进入A/D转化芯片SAA711A,SAA711A发生的数字视频信号、操控信号和状况信号送入操控处理芯片XC3142,以供XC3142取得各种采样信息,并对得到的数据与布景数据做差,然后将数字视频信号写入到FIFO里边,当FIFO里边的数据到达半满(此处半满状况对应视频一帧的数据),FIFO半满标志为0(低电平),XC3142检测到FIFO半满标志为0时,向USB操控芯片发送中止(Interrupt)信号,PC终端取得中止恳求后开端从FIFO里边读取数据。

2 USB接口的驱动程序与运用软件开发

USB运用体系软件开发分为两部分:主机操作体系上的客户驱动程序以及主机运用软件。主机运用软件经过客户驱动程序与体系USBI(USB Device Interface)进行通讯,由体系发生USB数据的传送动作;固件则呼应各种来自体系的USB规范恳求,完结各种数据的交流作业和事情处理。

首要开发TUSB3210在主机中的驱动程序。运用WinDDK3.0开发了Win2000下的驱动程序,完结了操控传输、中止传输和批传输的规范接口函数。在运用程序开发中,用VC++编制完结运用程序。在编成完结中把USB设备当成文件来操作,运用CreateFile得到USB句柄,用DeviceIoControl来进行操控传输,用ReadFile、WriteFile进行批量传输。

运用软件的结构如图2所示:

运用软件程序的根本流程如下:

1)翻开通讯通道,即确认一个运用方针,并对每个运用方针创立一个体系方针。2)初始化硬件资源,即为每个体系方针分配数据缓存、数据收集器和数据显现方针。3)发动收集进程,行将图画读入数据缓存,并将缓存赋值给数组,经过对数组的处理完结对图画的处理,图画数据与数据显现相关联后就能够经过显现控件或窗体显现预处理后的成果。

3 视频方针切割算法在FPGA中的完结

视频监督体系的首要意图是盯梢人们感兴趣的视频方针,一般情况下摄像机固定在室内或许建筑物的高处,为此能够为布景在必定时间内静止不动。Pan 提出了一种根据布景信息的运动方针检测办法[4],运用高阶统计量来重建布景,该办法能够较好的检测到运动方针,可是布景重建速度较慢,使得难以运用于实践视频监督体系,为此本文提出了一种新的布景重建办法,并运用VHDL言语在FPGA中完结了该算法,提高了布景重建速度。

布景图画重建

在布景重建中,引进布景置信度图画为C(x1,x2),它的掩膜图画为MC(x1,x2),重建布景图画为B(x1,x2),布景标明图画为BL(x1,x2)。假如C(x1,x2)大于预订的一个门限,则在视频帧中像素(x1,x2)为布景的概率更大,假如小于该门限则像素(x1,x2)为运动方针的概率相对较大。BL(x1,x2)是一个二值图画,用于标明对应像素的布景是否能重建,即:BL(x1,x2)=1,表明(x1,x2) 像素布景成功重建,不然失利。

考虑接连N帧图画s(x1,x2,k),s(x1,x2,k-1),…,s(x1,x2,k-N),对应的N-1个相邻帧差图画别离为d(x1,x2,k,k-1),d(x1,x2,k-1,k-2),…,d(x1,x2,k+1-N,k-N),则C(x1,x2),MC(x1,x2),B(x1,x2)和BL(x1,x2)的生成进程如下:

1) 初始化: 对每一个(x1,x2),C(x1,x2)=0 ,MC(x1,x2)=0,B(x1,x2)=0,BL(x1,x2)=0,n=0;

2) 考虑(x1,x2),假如MC(x1,x2)=1,至2)考虑下一个像素;不然至3);

3) 关于(x1,x2),假如d(x1,x2,k-n,k-n-1)Th1,则C(x1,x2)=0;

4) 假如C(x1,x2)》Th2,则MC(x1,x2)=1,到5);不然至6);

5) B(x1,x2)=[ s(x1,x2,k-n)+…+ s(x1,x2,k-n+Th2)]/Th2,BL(x1,x2)=1;

6) 假如n 其间Th1和 Th2别离为预先设置的门限,本实验中Th1=20,Th2=10。

视频方针切割

在视频切割中本体系选用类间方差阈值切割[5]法,这种办法是由最小二乘法推导得到的,此办法具有简略易于完结的长处。

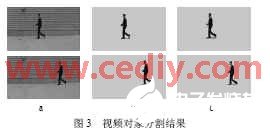

在后处理进程中,为了去除孤立点和填充空泛,在对视频图画帧差图画阈值切割完结后,进行数学形态学的开、闭和区域标明运算。视频方针切割实验成果如图3所示。

图3中a是一段视频图画列中的两帧图画;c是运用Pan办法的视频方针实时切割成果;b是运用本文的办法的方针切割成果。比较图3中 b、c可看出,本办法较Pan办法有更好的方针概括完整性和方针概括内方针相关点的连通性。本算法在一般PC机(PenTIum3 800M CPU ,256M DDRAM)上运转,视频图画为规范的CIF(288*384),256级灰度是非图画,运用本文算法其收集检测速率为24帧/s,运用Pan办法的速率为10帧/s。

4 定论

运用FPGA和USB操控芯片完结了实时视频监督收集体系,结合布景重建的办法能够完结视频图画的实时接连收集(每秒收集24帧视频图画)和视频方针切割的要求;改善后的布景重建和视频方针切割算法,较Pan办法有更好的检测作用和更快的切割速度。

责任编辑:gt