CPLD和FPGA都是咱们常常会用到的器材。有的说有装备芯片的是FPGA,没有的是CPLD;有的说逻辑资源多的是FPGA,少的是CPLD;有的直接就不做差异,把他们都叫做FPGA。那么两者到底有什么差异呢?下面咱们就以Altera公司的CPLD和FPGA为例来说说两者的差异。

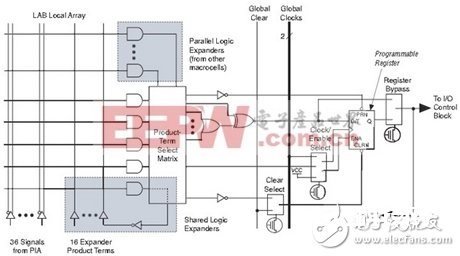

首要咱们看一下CPLD的芯片结构,搞清楚CPLD是由哪几部分组成的。下图是MAX系列CPLD的芯片结构图:

从图中能够清楚的看出来CPLD首要由三部分组成:Macro cell(宏单元),PIA(可编程连线),和IO Control Block(IO操控块)。每个宏单元都与GCLK(大局时钟)OE(输出使能)GCLR(清零)等操控信号直接相连,而且延时相同。各宏单元之间也由固定长度的金属线互连,这样确保逻辑电路的延时固定。其间宏单元模块是CPLD的逻辑功用完结单元,是器材的底子单元,咱们规划的逻辑电路便是由宏单元详细完结的。下面咱们再来看看宏单元的详细结构:

一个宏单元首要包括了LAB Local Array(逻辑阵列),Product-Term Select Matrix(乘积项挑选矩阵)和一个可编程D触发器组成。其间逻辑阵列的每一个交叉点都能够经过编程完结导通然后完结与逻辑,乘积项挑选矩阵可完结或逻辑。这两部分协同作业,就能够完结一个完好的组合逻辑。输出能够挑选经过D触发器,也能够对触发器进行旁路。经过这个结构能够发现,CPLD十分适宜完结组合逻辑,再合作后边的触发器也能够完结必定的时序逻辑。

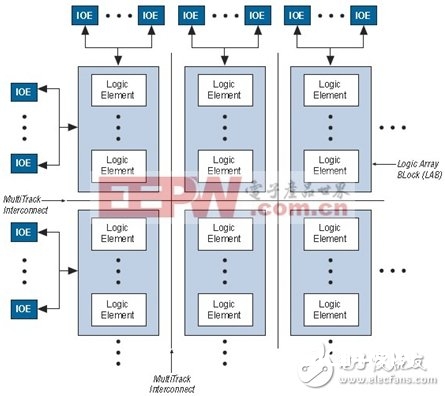

咱们再来以cyclone系列为例看看FPGA的内部结构:

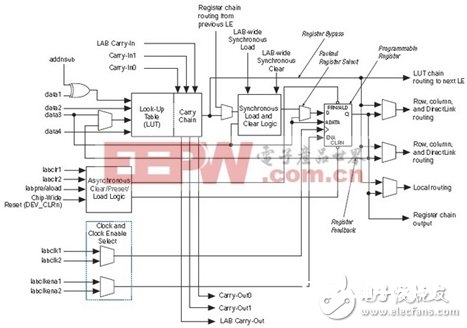

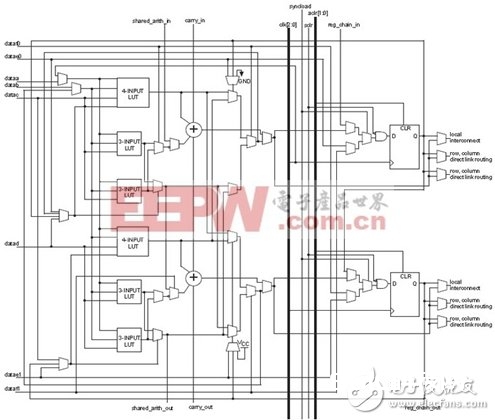

FPGA内部首要便是由LAB单元,连线和IO单元组成。一个LAB单元又包括若干个LE模块。LE模块是CycloneFPGA的底子逻辑单元,下图是LE模块的详细结构:

初看上去如同比较杂乱,其实最首要的部分便是LUT查找表模块,以及后边的D触发器。其他都是一些清零进位旁路等等操控信号逻辑。也便是说查找表是FPGA最底子的逻辑单元。Cyclone FPGA运用的是4输入LUT查找表。咱们规划的逻辑电路终究都是经过EDA东西把一切或许的成果计算出来然后储存在查找表里边。每次依据输入信号查找对应的成果,然后输出就能够了。也便是说FPGA的作业更像是一个RAM,依据不同的输入信号(地址)输出相应的数据。

经过上面的结构图比较咱们就能够清楚的看出来CPLD是由实实在在的组合电路组成的,而FPGA说到底便是一个巨大的查找表!也正是这个底子的差异造成了CPLD和FPGA各方面的不同。除了Altera以外,首要的CPLD和FPGA出产厂商还有Xilinx,Actel,LatTIce以及Atmel等。各家公司的产品各有特点,在架构上会略有差异,但底子原理都是相同的。下面咱们收拾一下CPLD和FPGA的首要差异:

1) CPLD的逻辑阵列更适宜可重复编程的EEPROM或Flash技能来完结。而FPGA显然是运用SRAM技能更适宜。

2) 由所以EEPROM或许Flash工艺决议了CPLD是有必定的擦写次数约束的。而FPGA在实践运用中简直能够说是无装备次数约束。

3) CPLD因为选用的是EEPROM或许Flash工艺所以装备掉电后不丢掉,也就不需求外挂装备芯片。而FPGA选用的是SRAM工艺,装备在掉电后就没有了,因而需求一个外部装备芯片。

4) CPLD的安全性更高。因为装备芯片的存在,FPGA的保密性就会比CPLD略差。逻辑数据有或许被读取。(当然FPGA芯片会有必定的加密办法)

5) CPLD因为不需求上电重新装备,所以上电后能够立刻作业。而FPGA上电后需求装备时刻,逻辑量的巨细装备方法的差异也会影响装备时刻的长短。

6) 因为CPLD的接连式布线结构,决议了它的时序延时是均匀和固定的。而FPGA选用的分段式布线结构造成了延时不固定。

7) 因为工艺难度的差异,CPLD一般集成度较低,大多为几千门或几万门的芯片规划,做到几十万门现已很困难。而FPGA依据SRAM工艺,集成度更高,能够轻松做到几十万门乃至几百万门的芯片规划,最新的FPGA产品现已挨近千万门的规划。

8) 相同因为结构的差异,CPLD更适宜完结的是杂乱的组合逻辑,如编、译码的作业。而FPGA更适宜做杂乱的时序逻辑。换句话说便是FPGA更适宜触发器丰厚的逻辑结构,CPLD适宜于触发器有限可是乘积项丰厚的逻辑结构。

9) 也是因为工艺的原因,一般CPLD会比FPGA的功耗高。

当然以上仅仅CPLD和FPGA一般意义上的差异,技能是在不断开展中的,这些差异也不能混为一谈。跟着技能的开展,CPLD和FPGA也在不断的更新傍边。

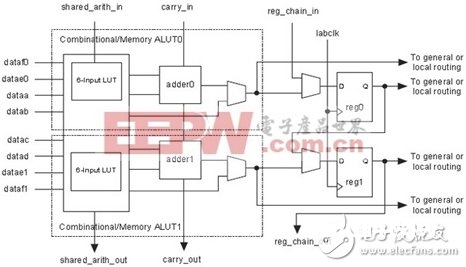

Altera在StraTIx III 系列FPGA今后的产品中调整了LE的结构,如下图:

从本来的一个4输入查找表加D触发器变成了两个6输入查找表加两个D触发器。再进一步细化查找表的结构图如下:

一个6输入查找表又能够细分为一个4输入查找表和两个3输入查找表。不管结构怎样变,仅仅出于对资源优化运用考虑的改动,底子的LUT查找表方法没有变。可是新出的MAX II系列和MAX V 系列CPLD则从底子上含糊了CPLD和FPGA的差异。经过阅览芯片手册咱们能够发现,两个系列的CPLD尽管姓名没有变,可是架构现已彻底是与FPGA相同的体系架构了,最小单元也变成了LUT查找表,宏单元现已消失不见了。或许和CPLD还能搭上联系的便是两个系列把装备电路集成到了芯片傍边,在实践运用中和原有的CPLD坚持了相同的运用习气。能够说两个系列的产品现已是披着CPLD外衣的FPGA了。

从技能的延续性上来看,可编程器材技能大致阅历了PROM-PLA-PAL-GAL-EPLD-CPLD和FPGA的开展过程,CPLD和FPGA是两个不同的开展分支。出产厂商好像在含糊CPLD和FPGA之间的差异。或许今后只剩下姓名的差异,两者会一致成一类器材,或许又会呈现更新的技能作为代替。不管技能怎么演进,作为工程师而言,咱们要做的便是去掌握每种器材的原理,优缺点和适用场景,然后在实践的项目中正确挑选,灵敏运用。

1、是否需求一起学习FPGA和CPLD?

许多同学有疑问,是否需求一起学习FPGA和CPLD,阿东在此表明,彻底没有必要,认为FPGA和CPLD的规划言语都是Verilog,至于CPLD和FPGA内部结构不一样,在编码阶段彻底看不出来,软件会依据CPLD仍是FPGA主动生成编程文件,所以学习的话主张值学习FPGA即可,FPGA学会了,底子就会用CPLD了。

2、现在的电路规划规划越来越大,动不动都是上万个或许几十万个乃至上百万个寄存器规划,这种规划下,CPLD底子不会考虑的,CPLD资源太少。