1:什么是同步逻辑和异步逻辑?

同步逻辑是时钟之间有固定的因果联系。异步逻辑是各时钟之间没有固定的因果联系。

同步时序逻辑电路的特色:各触发器的时钟端悉数衔接在一起,并接在体系时钟端,只需当时钟脉冲到来时,电路的状况才干改动。改动后的状况将一向坚持到下一个时 钟脉冲的到来,此刻不论外部输入 x有无改动,状况表中的每个状况都是安稳的。 异步时序逻辑电路的特色:电路中除能够运用带时钟的触发器外,还能够运用不带时钟的触发器和推迟元件作为存储元件,电路中没有一致的时钟,电路状况的改动由外部输入的 改动直接引起。

2:同步电路和异步电路的差异:

同步电路:存储电路中一切触发器的时钟输入端都接同一个时钟脉冲源,因而一切触发 器的状况的改动都与所加的时钟脉冲信号同步。异步电路:电路没有一致的时钟,有些触发器的时钟输入端与时钟脉冲源相连,这有这些触发器的状况改动与时钟脉冲同步,而其他的触发器的状况改动不与时钟脉冲同步。

3:时序规划的本质:

电路规划的难点在时序规划,时序规划的本质便是满意每一个触发器的树立/坚持时刻的而要求。

树立时刻:触发器在时钟上升沿到来之前,其数据输入端的数据有必要坚持不变的时刻。

坚持时刻:触发器在时钟上升沿到来之后,其数据输入端的数据有必要坚持不变的时刻。

不考虑时钟的skew,D2的树立时刻不能大于(时钟周期T – D1数据最迟抵达时刻T1max+T2max);坚持时刻不能大于(D1数据最快抵达时刻T1min+T2min);不然D2的数据将进入亚稳态并向后级电路传达。

4:为什么触发器要满意树立时刻和坚持时刻?

因为触发器内部数据的构成是需求必定的时刻的,假如不满意树立和坚持时刻,触发器将进入亚稳态,进入亚稳态后触发器的输出将不安稳,在0和1之间改动,这时需求经过一个恢复时刻,其输出才干安稳,但安稳后的值并不必定是你的输入值。这便是为什么要用两级触发器来同步异步输入信号。这样做能够避免因为异步输入信号关于本级时钟或许不满意树立坚持时刻而使本级触发器发生的亚稳态传抵达后边逻辑中,导致亚稳态的传达。

(比较简单了解的方法)换个方法了解:需求树立时刻是因为触发器的D段像一个锁存器在承受数据,为了安稳的设置前级门的状况需求一段安稳时刻;需求坚持时刻是因为在时钟沿到来之后,触发器要经过反响来所存状况,从后级门传到前级门需求时刻。

5:什么是亚稳态?为什么两级触发器能够避免亚稳态传达?

这也是一个异步电路同步化的问题。亚稳态是指触发器无法在某个规则的时刻段内抵达一个能够承认的状况。运用两级触发器来使异步电路同步化的电路其实叫做“一步同位器”,他只能用来对一位异步信号进行同步。两级触发器可避免亚稳态传达的原理:假定榜首级触发器的输入不满意其树立坚持时刻,它在榜首个脉冲沿到来后输出的数据就为亚稳态,那么鄙人一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时刻后有必要安稳下来,并且安稳的数据有必要满意第二级触发器的树立时刻,假如都满意了,鄙人一个脉冲沿到来时,第二级触发器将不会呈现亚稳态,因为其输入端的数据满意其树立坚持时刻。同步器有用的条件:榜首级触发器进入亚稳态后的恢复时刻 + 第二级触发器的树立时刻 《 = 时钟周期。

其他下降亚稳态的方法:

1 下降体系时钟频率

2 用反响更快的FF

3 引进同步机制,避免亚稳态传达(能够选用前面说的加两级触发器)。

4 改进时钟质量,用边缘改动快速的时钟信号

6:体系最高速度核算(最快时钟频率)和流水线规划思维:

同步电路的速度是指同步体系时钟的速度,同步时钟愈快,电路处理数据的时刻距离越短,电路在单位时刻内处理的数据量就愈大。假定 Tco是触发器的输入数据被时钟打入到触发器到数据抵达触发器输出端的延时时刻;Tdelay 是组合逻辑的延时;Tsetup是D触发器的树立时刻。假定数据已被时钟打入 D 触发器,那么数据抵达榜首个触发器的Q输出端需求的延时时刻是 Tco,经过组合逻辑的延时时刻为Tdelay,然后抵达第二个触发器的D端,要期望时钟能在第二个触发器再次被安稳地打入触发器,则时钟的推迟有必要大于Tco+Tdelay+Tsetup,也便是说最小的时钟周期 Tmin =Tco+Tdelay+Tsetup,即最快的时钟频率*Fmax=1/Tmin。FPGA 开发软件也是经过这种方法来核算体系最高工作速度 Fmax。因为 Tco 和Tsetup是由详细的器材工艺决议的,故规划电路时只能改动组合逻辑的推迟时刻Tdelay*,所以说缩短触发器间组合逻辑的延时时刻是进步同步电路速度的关键所在。因为一般同步电路都大于一级锁存,而要使电路安稳作业,时钟周期有必要满意最大延时要求。故只需缩短最长延时途径,才干进步电路的作业频率。能够将较大的组合逻辑分解为较小的N块,经过恰当的方法均匀分配组合逻辑,然后在中心刺进触发器,并和原触发器运用相同的时钟,就能够避免在两个触发器之间呈现过大的延时,消除速度瓶颈,这样能够进步电路的作业频率。这便是所谓”流水线”技能的根本规划思维,即原规划速度受限部分用一个时钟周期完结,选用流水线技能刺进触发器后,可用 N 个时钟周期完结,因而体系的作业速度能够加速,吞吐量加大。留意,流水线规划会在原数据通路上参加延时,别的硬件面积也会稍有添加。

比如:给了reg的setup,hold时刻,求中心组合逻辑的delay规模 :Delay 《 period – setup – hold

7:时序束缚的概念和根本战略?

时序束缚首要包含周期束缚,偏移束缚,静态时序途径束缚三种。经过附加时序束缚能够归纳布线东西调整映射和布局布线,使规划抵达时序要求。附加时序束缚的一般战略是先附加大局束缚,然后对快速和慢速破例途径附加专门束缚。附加大局束缚时,首要界说规划的一切时钟,对各时钟域内的同步元件进行分组,对分组附加周期束缚,然后对 FPGA/CPLD 输入输出PAD 附加偏移束缚、对全组合逻辑的 PAD TO PAD途径附加束缚。附加专门束缚时,首要束缚分组之间的途径,然后束缚快、慢速破例途径和多周期途径,以及其他特别途径。

8:附加束缚的效果?

效果:

1:进步规划的作业频率(削减了逻辑和布线延时);

2:取得正确的时序剖析陈述;(静态时序剖析东西以束缚作为判别时序是否满意规划要求的规范,因而要求规划者正确输入束缚,以便静态时序剖析东西能够正确的输出时序陈述)

3:指定 FPGA/CPLD 的电气规范和引脚方位。

9:FPGA 规划工程师尽力的方向:

SOPC,高速串行 I/O,低功耗,可靠性,可测验性和规划验证流程的优化等方面。跟着芯片工艺的进步,芯片容量、集成度都在添加,FPGA规划也朝着高速、高度集成、低功 耗、高可靠性、高可测、可验证性开展。芯片可测、可验证,正在成为杂乱规划所必备的条件,尽量在上板之前查出bug,将发现 bug 的时刻提早,这也是一些公司花大力气规划仿真 渠道的原因。别的跟着单板功用的进步、本钱的压力,低功耗也逐步进入FPGA 规划者的 考虑规模,完结相同的功用下,考虑怎么能够使芯片的功耗最低,听说 altera、xilinx 都在依据自己的芯片特色收拾怎么下降功耗的文档。高速串行 IO 的运用,也丰厚了 FPGA 的运用规模,象 xilinx 的 v2pro中的高速链路也逐步被运用。总归,学无止境,当把握必定概念、方法之后,就要开端考虑 FPGA 其它方面的问题了。

10:关于多位的异步信号怎么进行同步?

对以一位的异步信号能够运用“一位同步器进行同步”,而关于多位的异步信号,能够选用如下方法:

1:能够选用坚持寄存器加握手信号的方法(多数据,操控,地址);

2:特 殊的详细运用电路结构,依据运用的不同而不同 ;

3:异步FIFO。(最常用的缓存单元是 DPRAM)

11:FPGA和CPLD的差异?

FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用处的电路,专门为一个用户规划和制作的。依据一个用户的特定要求,能以低研发本钱,短、交货周期供货的全定制,半定制集成电路。与门阵列等其它ASIC(ApplicaTIon Specific IC)比较,它们又具有规划开发周期短、规划制作本钱低、开发东西先进、规范产品无需测验、质量安稳以及可实时在线查验等长处。

CPLD FPGA

内部结构 Product-term Look-up Table

程序存储 内部EEPROM SRAM,外挂EEPROM

资源类型 组合电路资源丰厚 触发器资源丰厚

集成度 低 高

运用场合 完结操控逻辑 能完结比较杂乱的算法

速度 慢 快

其他资源 - PLL、RAM和乘法器等

保密性 可加密 一般不能保密

12:锁存器(latch)和触发器(flip-flop)差异?

电平灵敏的存储器材称为锁存器。可分为高电平锁存器和低电平锁存器,用于不一起钟之间的信号同步。有穿插耦合的门构成的双稳态的存储原件称为触发器。分为上升沿触发和下降沿触发。能够以为是两个不同电平灵敏的锁存器串连而成。前一个锁存器决议了触发器的树立时刻, 后一个锁存器则决议了坚持时刻。

13:FPGA 芯片内有哪两种存储器资源?

FPGA 芯片内有两种存储器资源:一种叫 block ram,另一种是由 LUT 装备成的内部存储器(也便是分布式 ram)。 Block ram 由必定数量固定巨细的存储块构成的,运用 BLOCK RAM 资源不占用额定的逻辑资源,并且速度快。可是运用的时分耗费的 BLOCK RAM 资源是其块巨细的整数倍。

14:什么是时钟颤动?

时钟颤动是指芯片的某一个给定点上时钟周期发生暂时性改动,也便是说时钟周期在不同的周期上或许加长或缩短。它是一个均匀值为 0 的均匀变量。

15:FPGA 规划中对时钟的运用?(例如分频等)

FPGA 芯片有固定的时钟路由,这些路由能有削减时钟颤动和误差。需求对时钟进行相位移动或变频的时分,一般不允许对时钟进行逻辑操作,这样不只会添加时钟的误差和颤动, 还会使时钟带上毛刺。一般的处理方法是选用 FPGA芯片自带的时钟管理器如 PLL,DLL 或 DCM,或许把逻辑转换到触发器的 D 输入(这些也是对时钟逻辑操作的代替计划)。

16:FPGA 规划中怎么完结同步时序电路的延时?

首要说说异步电路的延时完结:异步电路一半是经过加 buffer、两级与非门等(我还没用过所以也不是很清楚),但这是不合适同步电路完结延时的。在同步电路中,关于比较大的和特别要求的延时,一半经过高速时钟发生计数器,经过计数器来操控延时;关于比较小的延时,能够经过触发器打一拍,不过这样只能推迟一个时钟周期。

17:FPGA 中能够归纳完结为 RAM/ROM/CAM 的三种资源及其留意事项?

三种资源:block ram;触发器(FF),查找表(LUT); 留意事项:

1:在生成 RAM 等存储单元时,应该首选 block ram资源;其原因有二:第 一:运用 block ram 等资源,能够节省更多的 FF 和 4-LUT 等底层可编程单元。运用 block ram 能够说是“不必白不必”,是最大程度发挥器材效能,节省本钱的一种体现; 第二:block ram 是一种能够装备的硬件结构,其可靠性和速度与用LUT 和 register 构建的存储器更有优势。

2:澄清 FPGA 的硬件结构,合理运用 block ram 资源;

3:剖析block ram 容量,高效运用 block ram 资源;

4:分布式 ram 资源(distribute ram)

18:什么是”线与”逻辑,要完结它,在硬件特性上有什么详细要求?

线与逻辑是两个输出信号相连能够完结与的功用。在硬件上,要用 oc 门来完结,因为不必 oc 门或许使灌电流过大,而烧坏逻辑门。一起在输出端口应加一个上拉电阻。Oc 门便是集电极开路门。

19:什么是竞赛与冒险现象?怎样判别?怎么消除?

在组合电路中,某一输入变量经过不同途径传输后,抵达电路中某一集合点的时刻有先有后,这种现象称竞赛;因为竞赛而使电路输出发生瞬时过错的现象叫做冒险。 (也便是因为竞赛发生的毛刺叫做冒险)。判别方法:代数法(假如布尔式中有相反的信号则或许发生竞赛和冒险现象);卡诺图:有两个相切的卡诺圈并且相切处没有被其他卡诺圈围住,就有 或许呈现竞赛冒险;实验法:示波器观测;

解决方法:

1:加滤波电路,消除毛刺的影响;

2:加选通讯号,避开毛刺;

3:添加冗余项消除逻辑冒险。

20:Xilinx中与大局时钟资源和DLL相关的硬件原语:

常用的与大局时钟资源相关的Xilinx器材原语包含:IBUFG, IBUFGDS,BUFG,BUFGP, BUFGCE, BUFGMUX,BUFGDLL,DCM等。

HDL言语是分层次的、类型的,最常用的层次概念有体系与规范级、功用模块级,行为级,寄存器传输级和门级。

21:查找表的原理与结构?

查找表(look-up-table)简称为LUT,LUT本质上便是一个RAM。现在FPGA中多运用4输入的LUT,所以每一个LUT能够当作一个有 4位地址线的16×1的RAM。当用户经过原理图或HDL言语描绘了一个逻辑电路今后,PLD/FPGA开发软件会主动核算逻辑电路的一切或许的成果,并把成果事前写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可

22:ic规划前端到后端的流程和eda东西?

规划前端也称逻辑规划,后端规划也称物理规划,两者并没有严厉的边界,一般涉及到与工艺有关的规划便是后端规划。

1:规范拟定:客户向芯片规划公司提出规划要求。

2:详细规划:芯片规划公司(Fabless)依据客户提出的规范要求,拿出规划解决计划和详细完结架构,区分模块功用。现在架构的验证一般依据

systemC言语,对价后模型的仿真能够运用systemC的仿真东西。例如:CoCentric和Visual Elite等。

3:HDL编码:规划输入东西:ultra ,visual VHDL等

4:仿真验证:modelsim

5:逻辑归纳:synplify

6:静态时序剖析:synopsys的Prime TIme

7:方法验证:Synopsys的Formality.

23:你知道那些常用逻辑电平?TTL与COMS电平能够直接互连吗?

常用逻辑电平:TTL、CMOS、LVTTL、LVCMOS、ECL(Emitter Coupled Logic)、PECL(Pseudo/PosiTIve Emitter Coupled Logic)、LVDS(Low Voltage DifferenTIal Signaling)、GTL(Gunning Transceiver Logic)、BTL(Backplane Transceiver Logic)、ETL(enhanced transceiver logic)、GTLP(Gunning Transceiver Logic Plus);RS232、RS422、RS485(12V,5V,3.3V);也有一种答案是:常用逻辑电平:12V,5V,3.3V。

TTL和CMOS不能够直接互连,因为TTL是在0.3-3.6V之间,而CMOS则是有在12V的有在5V的。CMOS输出接到TTL是能够直接互连。TTL接到 CMOS需求在输出端口加一上拉电阻接到5V或许12V。cmos的凹凸电平别离为:Vih》=0.7VDD,Vil《=0.3VDD;Voh》=0.9VDD,Vol《=0.1VDD.

ttl的为:Vih》=2.0v,Vil《=0.8v;Voh》=2.4v,Vol《=0.4v.

用cmos可直接驱动ttl;加上拉电阻后,ttl可驱动cmos.

1、当TTL电路驱动COMS电路时,假如TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需求在TTL的输出端接上拉电阻,以进步输出高电平的值。

2、OC门电路有必要加上拉电阻,以进步输出的高电平值。

3、为加大输出引脚的驱动才干,有的单片机管脚上也常运用上拉电阻。

4、在COMS芯片上,为了避免静电形成损坏,不必的管脚不能悬空,一般接上拉电阻发生下降输入阻抗,供给泄荷通路。

5、芯片的管脚加上拉电阻来进步输出电平,然后进步芯片输入信号的噪声容限增强抗搅扰才干。

6、进步总线的抗电磁搅扰才干。管脚悬空就比较简单承受外界的电磁搅扰。

7、长线传输中电阻不匹配简单引起反射波搅扰,加上下拉电阻是电阻匹配,有用的按捺反射波搅扰。 上拉电阻阻值的挑选准则包含:

1、从节省功耗及芯片的灌电流才干考虑应当满意大;电阻大,电流小。

2、从保证满意的驱动电流考虑应当满意小;电阻小,电流大。

3、关于高速电路,过大的上拉电阻或许边缘变陡峭。归纳考虑以上三点,一般在1k到10k之间选取。对下拉电阻也有相似道理。

OC门电路有必要加上拉电阻,以进步输出的高电平值。 OC门电路要输出“1”时才需求加上拉电阻不加根本就没有高电平。在有时咱们用OC门作驱动(例如操控一个 LED)灌电流作业时就能够不加上拉电阻 。OC门能够完结“线与”运算。 OC门便是集电极开路输出。 总归加上拉电阻能够进步驱动才干。

24:IC规划中同步复位与异步复位的差异?

同步复位在时钟沿采复位信号,完结复位动作。异步复位不论时钟,只需复位信号满意条件,就完结复位动作。异步复位对复位信号要求比较高,不能有毛刺,假如其与时钟联系不确定,也或许呈现亚稳态。

25:MOORE 与 MEELEY状况机的特征?

Moore 状况机的输出仅与当时状况值有关, 且只在时钟边缘到来时才会有状况改动。

Mealy 状况机的输出不只与当时状况值有关, 并且与当时输入值有关。

26:多时域规划中,怎么处理信号跨时域?

不同的时钟域之间信号通讯时需求进行同步处理,这样能够避免新时钟域中榜首级触发器的亚稳态信号对下级逻辑形成影响。信号跨时钟域同步:当单个信号跨时钟域时,能够选用两级触发器来同步;数据或地址总线跨时钟域时能够选用异步fifo来完结时钟同步;第三种方法便是选用握手信号。

27:说说静态、动态时序模拟的优缺点?

静态时序剖析是选用尽头剖析方法来提取出整个电路存在的一切时序途径,核算信号在这些途径上的传达延时,查看信号的树立和坚持时刻是否满意时序要求,经过对最大途径延时和最小途径延时的剖析,找出违反时序束缚的过错。它不需求输入向量就能尽头一切的途径,且工作速度很快、占用内存较少,不只能够对芯片规划进行全面的时序功用查看,并且还可运用时序剖析的成果来优化规划,因而静态时序剖析现已越来越多地被用到数字集成电路规划的验证中。

动态时序模拟便是一般的仿真,因为不或许发生齐备的测验向量,掩盖门级网表中的每一条途径。因而在动态时序剖析中,无法露出一些途径上或许存在的时序问题;

28:为什么一个规范的倒相器中P管的宽长比要比N管的宽长比大?

和载流子有关,P管是空穴导电,N管是电子导电,电子的迁移率大于空穴,相同的电场下,N管的电流大于P管,因而要增大P管的宽长比,使之对称,这样才干使得两者上升时刻下降时刻持平、凹凸电平的噪声容限相同、充电放电的时刻持平。

29:latch与register的差异,为什么现在多用register.行为级描绘中latch怎么发生的?

latch是电平触发,register是边缘触发,register在同一时钟边缘触发下动作,契合同步电路的规划思维,而latch则归于异步电路规划,往往会导致时序剖析困难,不恰当的运用latch则会很多糟蹋芯片资源。

30:状况图是以几何图形的方法来描绘时序逻辑电路的状况搬运规则以及输出与输入的联系。

31:sram,falsh memory,及dram的差异?

sram:静态随机存储器,存取速度快,但容量小,掉电后数据会丢掉,不像DRAM需求不断的REFRESH,制作本钱较高,一般用来作为快取(CACHE) 回忆体运用

flash:闪存,存取速度慢,容量大,掉电后数据不会丢掉

dram:动态随机存储器,有必要不断的从头的加强(REFRESHED)电位差量,不然电位差将下降至无法有满意的能量体现每一个回忆单位处于何种状况。价格比sram**廉价,但拜访速度较慢,耗电量较大,常用作核算机的内存**运用。

32:有四种复用方法,频分多路复用,写出别的三种?

四种复用方法:频分多路复用(FDMA),时分多路复用(TDMA),码分多路复用(CDMA),波分多路复用(WDMA)

33:基尔霍夫定理的内容

基尔霍夫规律包含电流规律和电压规律:

电流规律:在集总电路中,任何时刻,对任一节点,一切流出节点的支路电流的代数和恒等于零。

电压规律:在集总电路中,任何时刻,沿任一回路,一切支路电压的代数和恒等于零。

34:描绘反响电路的概念,罗列他们的运用。

反响,便是在电路体系中,把输出回路中的电量输入到输入回路中去。

反响的类型有:电压串联负反响、电流串联负反响、电压并联负反响、电流并联负反响。

负反响的长处:下降扩大器的增益灵敏度,改动输入电阻和输出电阻,改进扩大器的线性和非线性失真,有用地扩展扩大器的通频带,主动调节效果。

电压负反响的特色:电路的输出电压趋向于坚持稳定。 电流负反响的特色:电路的输出电流趋向于坚持稳定。

35:有源滤波器和无源滤波器的差异

无源滤波器:这种电路首要有无源元件R、L和C组成

有源滤波器:集成运放和R、C组成,具有不必电感、体积小、重量轻等长处。

集成运放的开环电压增益和输入阻抗均很高,输出电阻小,构成有源滤波电路后还具有必定的电压扩大和缓冲效果。但集成运放带宽有限,所以现在的有源滤波电路的作业频率难以做得很高。

36:什么叫做OTP片、掩膜片,两者的差异安在?

OTP means one time program,一次性编程 MTP means multi time program,屡次性编程

OTP(One Time Program)是MCU的一种存储器类型

MCU按其存储器类型可分为MASK(掩模)ROM、OTP(一次性可编程)ROM、FLASHROM等类型。

MASKROM的MCU价格廉价,但程序在出厂时现已固化,合适程序固定不变的运用场合;

FALSHROM的MCU程序能够重复擦写,灵活性很强,但价格较高,合适对价格不灵敏的运用场合或做开发用处;

OTP ROM的MCU价格介于前两者之间,一起又具有一次性可编程才干,合适既要求必定灵活性,又要求低本钱的运用场合,尤其是功用不断创新、需求敏捷量产的电子产品。

37、单片机上电后没有工作,首要要查看什么?

首要应该承认电源电压是否正常。用电压表丈量接地引脚跟电源引脚之间的电压,看是否是电源电压,例如常用的5V。

接下来便是查看复位引脚电压是否正常。别离丈量按下复位按钮和铺开复位按钮的电压值,看是否正确。

然后再查看晶振是否起振了,一般用示波器来看晶振引脚的波形,留意应该运用示波器探头的“X10”档。另一个方法是丈量复位状况下的IO口电平,按住复位键不放,然后丈量IO口(没接外部上拉的P0口在外)的电压,看是否是高电平,假如不是高电平,则八成是因为晶振没有起振。 别的还要留意的当地是,假如运用片内ROM的话(大部分状况下如此,现在现已很少有用外部扩ROM的了),必定要将EA引脚拉高,不然会呈现程序乱跑的状况。有时用仿真器能够,而烧入片子不可,往往是因为EA引脚没拉高的原因(当然,晶振没起振也是原因只一)。

经过上面几点的查看,一般即可排除故障了。假如体系不安稳的话,有时是因为电源滤波欠好导致的。在单片机的电源引脚跟地引脚之间接上一个0.1uF的电容会有所改进。假如电源没有滤波电容的话,则需求再接一个更大滤波电容,例如220uF的。遇到体系不安稳时,就能够并上电容试试(越接近芯片越好)。

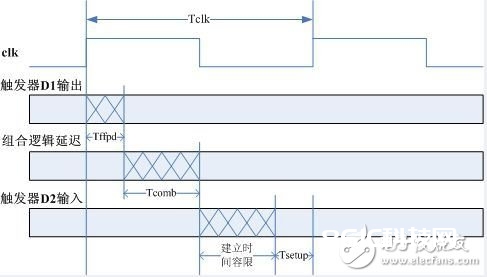

38: 时钟周期为 T,触发器 D1 的树立时刻最大为 T1max,最小为 T1min。组合逻辑电路最大推迟为 T2max,最小为 T2min。问:触发器 D2 的树立时刻 T3 和坚持时刻 T4 应满意什么条件?

树立时刻容限:相当于维护时刻,这儿要求树立时刻容限大于等于 0。

坚持时刻容限:坚持时刻容限也要求大于等于 0。

由上图可知,树立时刻容限=Tclk-Tffpd(max)-Tcomb(max)-Tsetup,依据树立时刻容限 ≥ 0 , 也 就 是

Tclk-Tffpd(max)-Tcomb(max)-Tsetup ≥ 0 , 可 以 得 到 触 发 器 D2 的 Tsetup ≤

Tclk-Tffpd(max)-Tcomb(max),因为标题没有考虑 Tffpd,所以咱们以为 Tffpd=0,所以得到

Tsetup≤T-T2max。

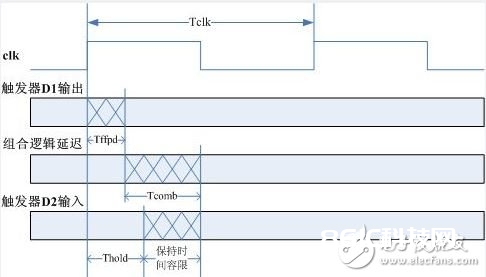

由上图可知,坚持时刻容限+Thold=Tffpd(min)+Tcomb(min),所以坚持时刻容限=

Tffpd(min)+Tcomb(min)-Thold,依据坚持时刻容限≥0,也便是 Tffpd(min)+Tcomb(min)-Thold≥0,得到触发器 D2 的 Thold≤Tffpd(min)+Tcomb(min),因为标题没有考虑 Tffpd,所以咱们 以为Tffpd=0,所以得到 Thold≤T2min。关于坚持时刻的了解便是,在触发器 D2 的输入信 号还处在坚持时刻的时分,假如触发器 D1的输呈现现已过组合逻辑抵达 D2 的输入端的话, 将会损坏 D2 原本应该坚持的数据。