ADP5033相关信息来自ADI官网,详细参数以官网发布为准,ADP5033供给信息可在查IC网查找相关供给商。

产品概况

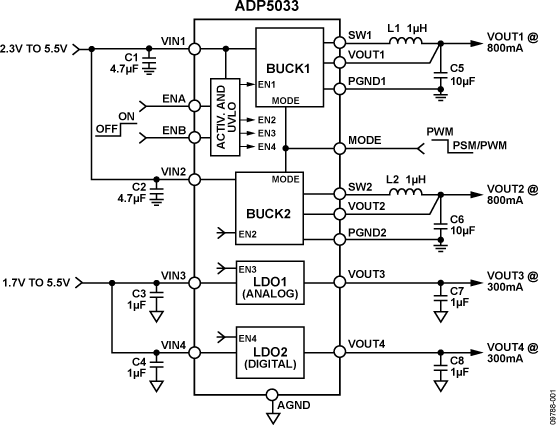

ADP5033在一个16引脚小型2 mm × 2 mm WLCSP封装中集成了两个高功能降压调节器和两个低压差调节器(LDO),可满意苛刻的功能和电路板空间要求。

降压调节器的高开关频率支撑小型多层外部器材,并使电路板空间降至最小。当MODE引脚设置为高电平时,降压调节器以强制PWM形式作业。当MODE引脚设置为低电平时,降压调节器以强制节能形式(PSM)作业。当负载挨近标称值且负载电流降至预界说阈值以下时,调节器以PSM形式作业,以便改进轻负载功率。

为下降输入电容要求和噪声,两个降压器以错相作业。

ADP5033 LDO的低静态电流、低压差和宽输入电压规模可延长便携式设备的电池使用时间。在频率高达10 kHz时,ADP5033 LDO能坚持60 dB以上的电源按捺功能,而所需的电压裕量则很低。

ADP5033中的调节器经过ENA和ENB引脚激活。ENA和ENB操控的详细通道由工厂编程设定。对使能引脚施加高电平将激活调节器。默许输出电压可在工厂编程设置,挑选规模广泛。

使用

- 适用于处理器、ASIC、FPGA和RF芯片组的电源

- 便携式仪器仪表和医疗设备

- 空间受限器材

优势和特色

- 输入电压规模:2.3 V至5.5 V

- 两个800 mA降压调节器和两个300 mA LDO

- 2 mm × 2 mm、16引脚小型WLCSP封装

- 调节器精度: ±1.8%

- 工厂可编程VOUTx

ADP5033电路图

ADP5033中文PDF下载地址

ADP5033下载链接地址:https://www.analog.com/media/cn/technical-documentation/data-sheets/ADP5033_cn.pdf

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/ziliao/beidong/41517.html