以太网接口通讯速度快,传输牢靠,运用和装备便利,关于20 Mb/s以下的码速率,100 Mb/s的网卡能够进行不丢包转发,选用TCP包格局还可使设备小型化,便于数据的转发,因此有必要扩展设备的以太网功用。

1 全体模块规划

1.1 体系规划

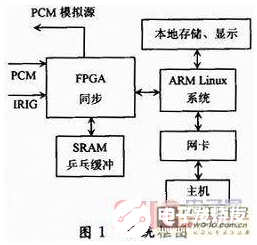

体系规划框图如图1所示。其间,采编器或接纳机解调输出的PCM信号及时钟输入到FPGA中进行帧同步,IRIG—B码信息也送到FPGA中进行解调,得到时刻信息。数据与时刻一同存入SRAM乒乓缓冲区中,到达必定巨细后,FPGA向ARM处理器发器中止,ARM中运转的Linux体系,将数据取走,进行TCP/IP打包,发送给接纳计算机。

在设备开端作业前,需求在计算机端进行参数设置,计算机TCP/IP包将参数发送给ARM处理器,由ARM处理器转发给FPGA。帧同步器的规划中,码速率为100b/s~10Mb/s,帧长为4~4 096Word,帧同步码组为4~32,ARM网卡为100Mb/s。

1.2 硬件完结

PCB选用6层结构,相邻布线层,水平笔直穿插,电路层与电源层独自分隔,供给杰出的电磁兼容特性。

1.2.1 FPGA

FPGA挑选EP1C12,为完结乒乓缓冲结构,选用SRAM为IS61LV25616。输入信号运用SMA线缆衔接,在传输进程中会引进衰减,信号输入输出易呈现阻抗不匹配的状况,选用AD8556构成射随器,对输入信号进行匹配,一起也增大模仿源的输出才能。

1.2.2 ARM

在此选用S3C2440,内核为ARM920T,最高频率为400 MHz,带MMU支撑操作体系。内存选用2×32 MB的SDRAM,存储选用128 MB NAND FLASH,网卡选用DM9000A。

1.2.3 ARM与FPGA的接口衔接

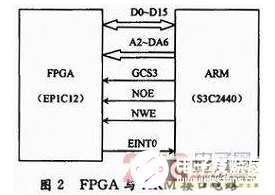

这儿选用总线接口,将FPGA作为一个存储设备挂在ARM的存储器总线上,如图2所示。

FPGA在ARM中开端地址为0x18000000,以4 B对齐,占用0x80个地址,地址规模为0x18000000~Ox1800007C,中止为EINT0。

在FPGA内部选用读/写指针来模仿FIFO,用一个地址来读取FPGA数据,其他地址用于装备帧同步器与模仿源的参数。

2 帧同步与B码解调

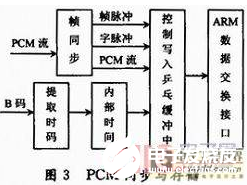

FPGA完结PCM数据的帧同步和解调B码,写入到乒乓SRAM缓冲区中,完结如图3所示。

2.1 帧同步模块

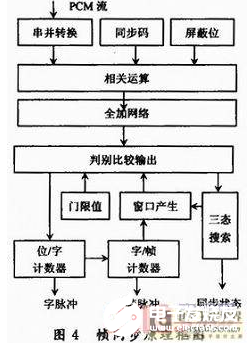

帧同步器依据帧同步码组的相关性和周期性,经过相关运算将同步码从PCM串行流中辨认出来,原理框图如图4所示。

PCM数据按时钟进行串/并转化,与本地帧同步码进行同或运算后再与上屏蔽位,由全加网络将相关运算成果按位相加计算成果中1的个数,大于门限值则表明或许接纳到了帧同步码。

为防止虚警和漏检,使帧同步器安稳牢靠作业,选用查找、校核、锁定三态逻辑。

体系开端时处于查找态,契合相关器输出,由查找态转入校核态。在预期检测窗口内没有帧码,从校核回来到查找态。接连经过校核数α,进入确定态。为防止帧同步码的漏检,接连漏检超越维护帧数β,帧同步才回来查找态,不然保持在确定态,帧脉冲由本地发生。

2.2 IRIG—B码解调

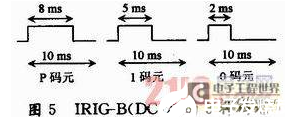

IRIG时刻序列码是一种串行码,共有3种码元,如图5所示。

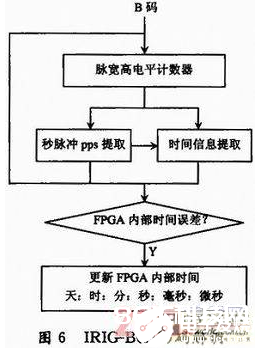

P码元是方位码元,接连2个P码为一帧的开端,第1个P码元界说为P0,第2个P码元为秒脉冲pps,上升沿为该秒的准时刻,时刻信息以BCD码顺次散布在这以后的码元中。解调时先进行pps的提取,再进行秒、分、时、天的信息提取,其流程如图6所示。

时钟频率为1 MHz,用计数器对输入信号的脉宽进行计数。8 ms,5 ms,2 ms脉宽计数为8 000,5 000,2 000。输入B码的脉宽会混有搅扰,晶振时钟也存在必定的差错,计数器的计时判别应起浮一个规模,设置门限为脉宽的85%~115%,当满意必定规模的数值时,别离输出P码,0码,1码信号。

FPGA中的时码发生“天:时:分:秒:毫秒:微秒”信息。解调出B码时,FPGA更新内部时刻,B码中不含毫秒与微秒信息,由FPGA依据秒脉冲信息的准时刻来生成。

3 FPGA驱动程序开发

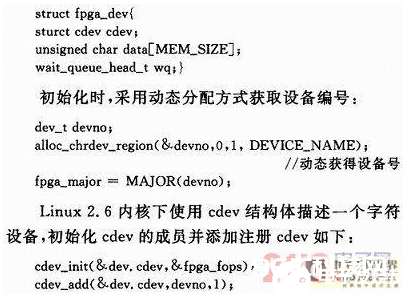

在Linux中,一切的硬件设备都像惯例文件相同进行翻开、封闭和读/写。把FPGA当作字符设备进行规划,驱动由设备加载与卸载,以及文件操作file_operation结构体中成员函数组成。

3.1 加载与卸栽设备驱动

FPGA设备驱动程序初始化流程为动态取得主设备号、字符设备注册和请求中止;卸载流程为刊出设备,开释设备编号。

界说一个设备结构体来表明FPGA,如下:

当用户程序读FPGA设备时,数据还未准备好,此刻驱动程序应该堵塞该进程,将其置入睡觉状况直到条件满意。此刻需求初始化一个等候行列头,对读进程的休眠和唤醒时运用:

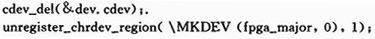

在卸载函数中,删去一个cdev,完结字符设备的刊出,然后开释设备编号:

3.2 文件接口操作

Linux为一切的设备文件都供给了一致的操作函数,FPGA设备驱动。file_operaTIons包括翻开函fpga_open、读函数fpga_read、设置参数函数fpga_ioctl和封闭设备函数fpga_release。

3.2.1 翻开与封闭FPGA设备

在翻开设备与封闭设备时会调用open函数与release函数,在open函数中,要对设备进行I/O内存资源映射及中止请求。

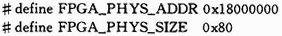

设备驱动程序中,需经过内存办理单元MMU将设备的虚拟地址映射到物理地址。依据FPGA在S3C2440中的物理地址,界说如下宏:

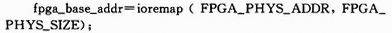

运用ioremap()对FPGA的I/O内存资源进行映射,把物理内存地址映射为一个内核指针:

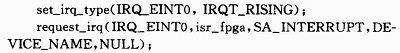

数据交换选用中止,需先设置硬件中止方法,然后向体系注册中止函数,完结如下:

FPGA衔接在ARM的EINT0上,isr_fpga为中止处理函数指针。当封闭FPGA设备时,需开释I/O内存,开释中止:

3.2.2 驱动程序控制接口Ioctl

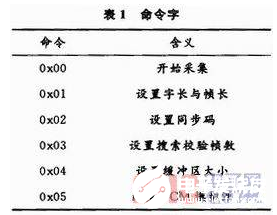

Ioctl用来设置FPGA中帧同步器和模仿源的参数,部分设置指令如表1所示。

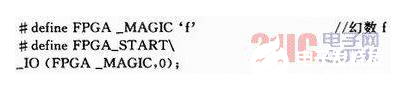

在此,选用一致的指令码方法,包括幻数、序数、传输方向、数据长度,运用宏_IO(),_IOR(),_IOW()和IOWR()辅佐生成,如指令0设置如下:

在Ioctl中,选用switeh(cmd)来完结对FPGA参数的设置及FPGA状况的读取。

3.2.3 中止函数及读函数

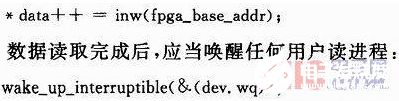

当FPGA发生中止时,依据缓冲区的巨细,中止函数循环对FPGA映射后的地址读取数据。ARM与FPGA接口为16位,运用inw读取,数据存放在驱动程序的缓冲区中:

应用程序读取数据时,调用read函数,参数buffer为用户空间缓冲区的指针,运用copy_to_user函数将数据从内核空间拷贝到用户空间,当设备中暂时没有数据时,读进程应当被休眠:

flag为一个标志位,当flag被中止函数设置为1时表明设备中有数据,此刻读进程可被换醒。

3.2.4 用户程序及测验

设备驱动完结后,需编写相应的用户程序来进行测验驱动程序和完结数据的网络转发。在用户程序中,读/写FPGA设备运用与一般文件相同的操作函数。移植Linux时装备好网卡的地址,然后运用Socket编程完结数据的TCP/IP转发,用遥测软件接纳到的数据测验如图7所示。

经过测验能够看到,同步码FDB18450被正确辨认,IRIG-B解码为当时时刻。

4 结语

在此,依据FPGA与ARM进行遥测数据的帧同步遥测数据的网络转发,充沛地运用了FPGA与ARM各自的特色,它可使FPGA+ARM在数据接纳处理中得到广泛应用。