在SoC体系的规划及运用进程中,对其内部行为的实时监控十分重要,现在遍及经过监控端和方针体系间的监控信息通讯来完结,UART常用作通讯信道。

方针SoC体系常运用中止办法或轮询办法获取监控通讯数据包,对其解析并进行相应数据操作后回复应对信息。中止办法中SoC需完结保存中止现场、调用中止服务程序、康复现场系列使命,上下文的切换占有了体系额定开支;轮询办法中,体系守时查看设备恳求,若有数据抵达则调用相应处理程序,固定的轮询周期增加了数据等候处理时刻,数据量较小时频频查询造成对CPU资源的糟蹋。

针对上述问题,提出一种的新监控办法,规划一个FPGA通讯体系,由其作为SoC与监控计算机数据交互的桥梁,担任完结在线监控的通讯进程,确保被调试体系和调试主机之间调试信息和指令的交互牢靠性,可防止方针SoC频频的处理通讯中止,进步其操控功用。监控功用完结机制与通讯体系首要模块的规划办法将被评论,经过比照嵌入式CPU在不同监控办法中的通讯时刻耗费,阐明该办法具有必定实用价值。

1 体系组成结构

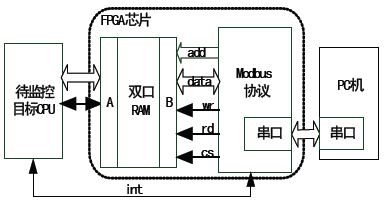

依据FPGA规划片上通讯体系如图1所示,其首要组成部分为Modbus解析模块和双口RAM存储模块。上位机宣布监控指令帧数据时,由Modbus模块完结指令帧的接纳、解析进程,并将待操作地址、数据等信息存入双口RAM中,方针CPU据此将本身内存映像区的相应数据一次搬入双口RAM,搬移结束后,Modbus协议模块进行应对数据组帧,并向监控上位机发回应对数据,完结对监控数据的实时牢靠收集。

图 1 通讯体系组成结构

2 依据双口RAM的数据交互规划

2.1 双口RAM定制及内存映射规划

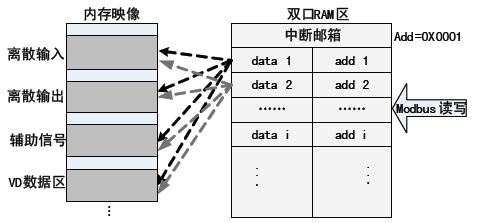

方针SoC中的待监控数据状况量在内存中的存储办法,可笼统表明为如图2中内存映像。

图 2 双口 RAM 的内存映射机制

双口RAM中存储当时待监控数据方针调集,是方针CPU内存映像区的一个数据子集。因为当时监控方针可随机落在内存映像区的恣意存储块上,双口RAM的内存映射办法选取为随机映射,如图2所示。

涣散存放于CPU内存映像区的监控方针,映射为双口RAM中的接连存储区。上位机依据Modbus协议与FPGA片上体系通讯时,拜访接连的地址单元,确保了数据拜访速度,进步体系的通讯功率。

2.2 双口RAM中的数据操作规划

2.2.1 上位机对双口RAM的读写操作

PC上位机为通讯建议方,经过串口与FPGA片上体系衔接,选用Modbus-RTU协议进行数据通讯,完结对运转参数的读取和写入等操作,完结监控功用。

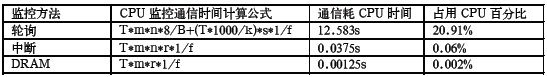

表 1 监控通讯进程占用 CPU 时刻

用户在人机界面输入本次待监控方针信息, 后台软件依据Modbus帧结构及约好的双口RAM内存映射机制,组成监控指令帧并经过串口宣布。FPGA片上体系对收到的指令帧进行解析,获取操作功用码、方针地址、数据包巨细等信息,据此向双口RAM区写入待操作数据地址集,写入结束后向方针CPU请求通讯中止。依据Modbus指令帧中给出的数据操作长度,一次可对多个数据单元进行读/写操作。