DMA(英文全称:Direct Memory Access,中文:直接内存拜访)是一种不经过CPU而直接从内存存取数据的数据交换形式。在DMA形式下,CPU只须向DMA控制器下达指令,让DMA控制器来处理数据的传送,数据传送完毕再把信息反馈给CPU,这样就很大程度上减轻了CPU资源占有率,能够大大节约体系资源。

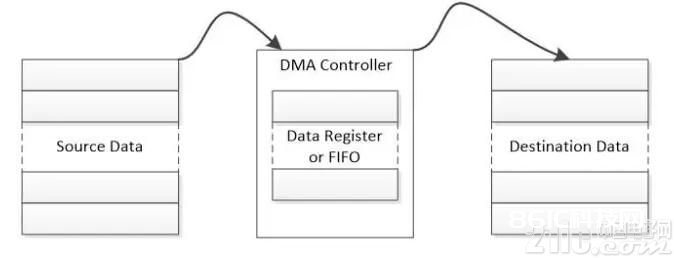

DMA的传输模型结构见下图:

Figure 1 DMA传输模型

从上图可知,运用DMA从源地址传输数据到意图地址,数据都必须经过DMA控制器内部的寄存器或FIFO作缓存,而不是在源和意图地之间直接传输,这是因为源和意图地点设备的传输速度不一样,接口也不一样,要习惯这些状况,数据在DMA控制器内的缓存是必不可少的,这样可使在低速设备传输数据时,高速设备可被开释并可被从头运用,这可看作是一种解耦,使低速设备和高速都能高效作业而不相互影响。

笔者在作业进程中,曾遇到一个有关DMA的issue,详细如下:在某个运用运用DMA进行大数据量传输进程中,经常呈现数据传输反常,查看体系的调试打印信息,发现DMA在阶段性传输完毕(会发生相应的中止)后,从头发动新阶段的DMA传输(运用相同的通道)时,有时会呈现请求的DMA通道还在活动状况的状况,导致后边的数据传输无法正常发动。依照一般的思路,驱动程序设置好参数,发动DMA后,就能够去做其他作业,中止的到来就意味着该次的DMA传输完毕了,但对立的是有时发现传输完毕的DMA通道却不在闲暇状况,要阐明的是,一切的DMA通道资源都是预先分配好的,不同驱动程序运用各自不同的通道,不会相互搅扰。开端以为是驱动程序没有规划好,呈现竞赛导致函数重入,但阅览整个驱动源码后,没有发现这方面的问题。

从头剖析整个DMA传输进程:数据从源设备到方针设备,中心是要经过DMA controller Data transfer register或FIFO这个中转站暂存,而中止发生的条件是只需源或意图地址更新到与告诉地址相同,这样傍边止发生时,最终的数据或许还在中转站内,传输还在进行傍边,因为最终的数据传输什么时候能真实完毕,取决于方针器材以及其时的总线裁定等状况,时刻比较随机,此刻中止服务函数从头发动新阶段传输前查看该通道时就有或许查询到DMA通道还处于忙状况,这样就会导致从头发动DMA通道失利而无法继续进行数据传输。

开始以为issue的发生是因为真实的数据传输完毕滞后于DMA中止的发生(这个应该是硬件规划的一个bug),因而处理的办法便是参加等候,这能够经过屡次重复查询来完成。依照这个思路,修正驱动程序,从头进行测验,问题没有复现,数据传输正常,这阐明以上的剖析揣度是正确的。

经过上面的比如能够看到,充沛了解DMA规划的一些硬件根本机理,对咱们在作业傍边处理一些实际问题仍是很有协助的。