规划电路时,许多工程师不会忘掉增加各式各样的维护电路,尤其在特别软弱的I/O口。或许你曾经没有注重到“高压脉冲”,今日这儿给咱们支招:怎样防止电路规划这些坑。

在产品规划过程中,咱们往往更注重产品的外观、功用、功能,而对一些细节没有给予满足的注重。许多时分,给产品形成重大问题的正是这些看似不起眼的细节问题。

就如咱们在规划P800isp的电源电路时,要点注重了电压幅值、纹波、负载调整率等硬性方针,而上电瞬间的状况被咱们忽视了。当咱们用P800isp对客户供给的方针板上的芯片进行编程调试时,发现一个古怪的现象:

当编程器上电安稳后再接上方针板时,就能够对方针芯片进行擦除、编程、校验;

当接上方针板后再给编程器上电时,对方针芯片的任何操作都会失利;

当接上方针板后再给编程器上电后,这个方针板后边不管是先上电再接线仍是先接线再上电,都会编程失利。

搭档以身试险,用手去接触编程失利的芯片,被烫得手指都起了泡。用万用表丈量发现编程失利的芯片电源脚和地现已短路了。丈量编程电源的电压正常。因此咱们依据经历估测很有可能是编程器上电时编程电源有反常高压输出将方针芯片击穿。用示波器捕获编程器上电瞬间编程电源Vout的波形证明了咱们的猜测。

如图1所示,编程器上电瞬间,编程电源Vout有高达20.4V、继续时刻长达150ms的脉冲输出到方针芯片。供电电源才3.3V的方针芯片明显无法接受这样的高压脉冲。

图1 上电瞬间Vout的反常输出

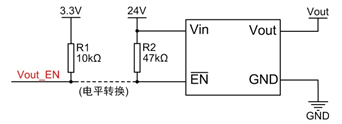

从图2的Vout电源电路的示意图看出Vout是由Vout_EN操控的,低电平使能Vout输出。Vout_EN上拉到3.3V高电平,上电瞬间默许应该禁能Vout输出的,怎样还会有这个高压脉冲输出呢?

图2 Vout电源电路示意图

从图1能够发现,Vout输出20.4V并继续近30ms后,Vout_EN才上拉到高电平禁能Vout输出,尔后Vout才逐步降低到0V。为什么Vout_EN要比Vout滞后30ms才有用,而不是一上电就有用呢?

咱们看下图3,3.3V是由24V转化成5V再转化而成的,因此3.3V的发生需求必定时刻,相应的Vout_EN也需求必定时刻才干有用。正是因为这个时刻差,Vout才干够输出20.4V的高压脉冲。

图4 3.3V电源示意图

要处理使能信号滞后的问题,最好的处理方案便是用输入电源Vin作为使能电平。当输入电源上电时,就能直接禁能Vout的输出。在Vout_EN和Vin使能电平之间参加电平转化电路,使3.3V电平的Vout_EN能够在程序运转后正常操控Vout的输出。通过改善后,上电瞬间的高压脉冲被完美的消除了。

图5 改善后的Vout电源电路

所以在产品的规划过程中,容不得半点忽略,具有匠心精力,才干打造出精品。