跟着社会出产与研讨规划对喷绘产品高速化的需求日积月累,传统的数字喷墨式印刷机现已不能满意这种需求。而大幅面高速五颜六色喷绘机不管是在数据的传输速度仍是在打印的质量上都超过了传统的数字喷墨式印刷机。可是,大幅面高速五颜六色喷绘机的技能并不是非常老练,还有许多的当地能够改进。

近年来,跟着微电子规划技能与工艺的开展,数字集成电路从电子管、晶体管、中小规划集成电路、超大规划集成电路逐渐开展到今日的专用集成电路(ASIC)。ASIC的呈现降低了产品的出产成本,提高了体系的可靠性,缩小了电路的物理尺度,推动了社会的数字化进程[1]。数字电路规划当顶用FPGA来完结FIFO的功用能够更好地处理并行性和实时性问题,并且用FPGA完结的FIFO更简单修正和测验,能够降低成本和缩短开发周期。

1 像素数据传输守时剖析

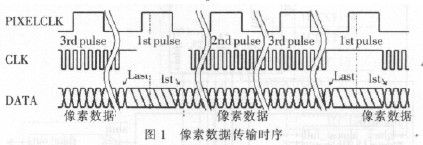

像素数据传输时序如图1所示,像素数据传输在CLK的同步下进行,每次传送256×2 bit,运用256个CLK时钟。在传输开端前和传输完毕后,CLK应该坚持在高电平。每次传输完后,等候3个接连的像素时钟(PIXELCLK),即焚烧信号,3个焚烧信号使存储在喷头中的像素数据完结焚烧输出。第一个焚烧脉冲有数据锁存的功用,在该脉冲往后,前次接纳的数据完结锁存,能够开端下一次的数据移位输入作业,虽然此刻上一次输入的像素数据还没有耗费完。因而,可完结数据传输和焚烧一起进行。在第一个焚烧脉冲到来期间,像素数据和像素时钟应该坚持不变。

2 像素数据格局

像素数据分为焚烧和不焚烧两种,焚烧的(喷出的)像素其数据要求为D2D1D0(D6D5D4)=111,不焚烧的(不喷出的)像素要求D2D1D0(D6D5D4)=000。因而,实践传输时可采用两条信号线,一条担任D2D1D0的像素,另一条担任D6D5D4的像素,而在数据进入喷头之前,将输入的1信号展开成111,0信号展开成000即可。这样可用两条信号线完结6条信号线的功用。

每次传送,一个喷头所需求的数据为512 bit,其间,第0和第511 bit有必要为0,实践完结510孔数据的传送,可是数据传送运用的是256个CLK时钟,每时钟传送2 bit。分作两条信号线传输,一条是D2D1D0担任256~511孔的数据传送,D6D5D4担任0~255孔的数据传送。这就要求有一种电路,先缓冲256~511孔的数据,再将0~255孔的数据与之兼并后一起传送到喷头。

如考虑图画的存储格局,喷头应该倒置,即510孔的方位在前,0孔的方位在后,即实践的像素数据的次序号与喷头的孔号相反,喷头的像素数据如表1所示。

3 整体完结

3.1 喷头接口模块

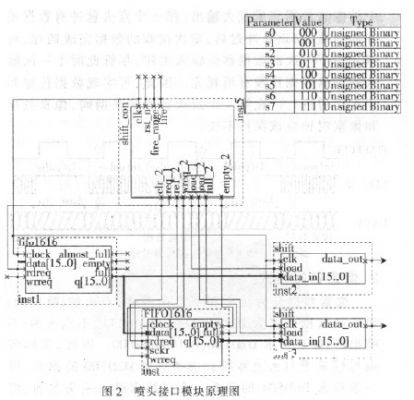

喷头接口模块接纳来自于上位机的打印图画数据,在喷头数据时钟clk的同步下,向喷头送出喷头数据。根据运动操控模块传出的当时方位和本身存储的打印方位,送出焚烧信号fire。

因为喷头要求将0~255喷孔和256~511喷孔的数据一起送出,因而,喷头接口应该至少能存储512个喷孔的数据,每喷孔1 bit数据,共64 B,32个半字(16 bit)。为确保实时性,这些数据应该经过缓冲与上位机接口,最好的缓冲便是FIFO。其规划原理图如图2所示。

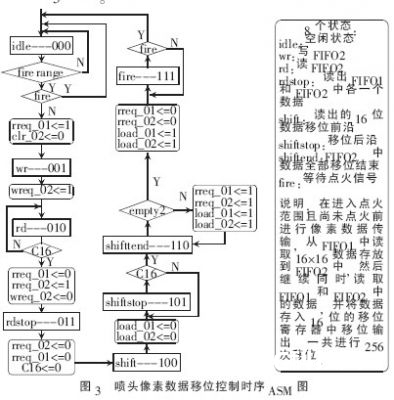

3.2 移位操控器

移位操控器担任从数据缓存FIFO1中读出数据,并按需求的次序装入到FIFO2中,在FIFO2装满的一起读取两个数据缓存中的数据并进行移位操作。操控器工作的另一个条件是上一个装入-焚烧周期完结,因而有必要在检测到焚烧信号变为低电平后才干触发。其规划ASM图如图3所示。

3.3 波形验证

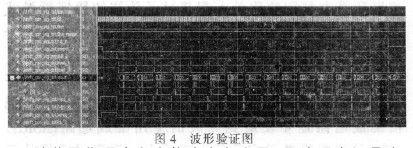

输出操控器完结输出数据的装载和移位输出的操控。具体要求是当数据向数据缓存FIFO1装载现已完结并抵达焚烧边际时,主动进行256 bit数据的装载和移位,到达0~511孔一起装入数据的意图。然后等候焚烧信号,当第一个焚烧信号往后,就可重复装入输出。其波形验证如图4所示。

跟着图画逐渐向大格局方向开展,不管研讨仍是出产都对上位机和打印机之间的数据传输速度要求越来越高。因而,不只要使用FIFO作为缓冲来处理喷头和上位机存在的像素数据方向相反的问题,并且要使用异步FIFO用不一起钟驱动读写的特性,使其主动读取USB芯片内的数据,然后大大提高数据传输速度,处理数据传输的实时性问题。该规划现已应用于实践开发项目中,并使大幅面高速五颜六色喷绘机的数据传输速率和图画正确性得到了极大的改进。