近几年来,跟着后PC年代的降临,具有简练、高效等特色的嵌入式体系得到了飞速的开展。嵌入式技能开展到今日已将各种计算机技能多层次、多方面的穿插融合在了一同。嵌入式体系加快了工业规划进程,降低了开发本钱及其危险,运用简洁,扩展灵敏,高效精简,可方便地应用于各工业范畴。 中止恳求选用边缘触发来进行中止检测,经过将信号送到特定的引线来检测中止。每条引线对应一个或许的硬件中止,由于体系不能辨认哪个设备运用中止线,所以当多个1个的设备被设置成运用同一个特定中止时就发生了紊乱。中止发生时,由专用的中止程序接纳体系,首先把一切的CPU寄存器内容保存到仓库里,并引导体系指向中止向量表。在中止程序履行后的一段时刻中,中止操控软件把仓库内容回来给寄存器,体系康复中止发生之前 的状况。如此段时刻中又有中止恳求,将形成中止的设备判别紊乱,从而会形成中止抵触、丢掉,乃至使得设置无法正常作业。因而,每个中止通常被分配给单一的设备,使中止无法同享。 传统办法中,扩展多个串行口是运用多个中止源;但在嵌入式体系中,花费很多的中止源来扩展串口无疑是很多的资源糟蹋。针对这种状况,为了节约严重的体系资源,本文提出一种完结高效多串口中止计划,可以运用单一的中止源来办理多个扩展串口,并保证多个串口中止的无漏检测与服务。

1 整体规划计划

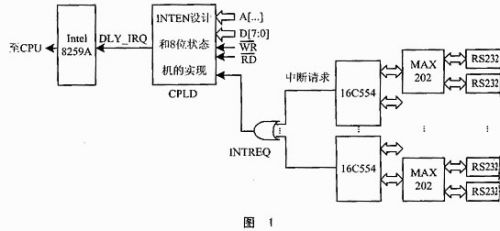

基本原理结构如图1所示。RS232串口经过驱动芯片MAX202转化成TTL电平,经过串口异步通讯器材16C554输出中止恳求,经过或门取得多个串口的中止恳求INTREQ,再经过CPLD与中止操控器相衔接。中止线INTREQ经过CPLD首要是在CPLD中做了一个1位的操控寄存器INTEN,用作中止答应操控位,而且依据16C554的中止恳求INTREQ和INTEN的状况来终究生成DLY_IRQ,向CPU宣布恳求。CPU实时呼应中止恳求DLY_IRQ。在中止服务过程中,CPU按次序逐一查看多个扩展的串口中止源,有中止恳求的就给予服务。当刚刚查看过的中止又出现时,一方面靠CPLD中的一位寄存器INTREQ锁存;另一方面,当上一中止服务完毕时,CPLD中的8位状况机保证了必定时刻的推迟。此延时中,中止操控把仓库内容回来给CPU寄存器,康复能取得呼应。这样,即便在多个串口中止密布发生的环境下,扩展的多个串行口仍可取得实时性和牢靠性较高的中止呼应。

2 硬件完结

(1)MAX202 Maxim公司的MAX202芯片是规范的RS232电平转化器,是契合RS232通讯规范的接口芯片;功耗低,集成度高,只用单一5V电源,每片有2个驱动器和2个接纳器,具有2组接纳和发送通道;悉数接口电路简略,牢靠性高,可完结TTL电平缓RS232电平的直接转化。

(2)16C554 16C554是集成异步通讯元件。在FIFO形式,传输和接纳前数据缓冲为16字节数据包,减了CPU的中止数量。包括4个改进16C550异步传输器材,使得串行I/O愈加牢靠。每个信道完结串行和并行2种衔接方法的转化;每个信道的状况可以经过CPU的操作读取,可以获取操作状况或任何的过错状况。三态输出为双向数据总线和操控总线供给TTL驱动才能、优先级中止体系操控、可编程的串行接口特性。

(3)8259A 8259A是可编程的中止操控芯片。每块芯片可办理8级向量中止, 具有8条中止恳求输入线IRQ0~IRQ7,1条外中止恳求输出线;具有4种首要作业方法,即全嵌套、循环优先级、特定屏蔽和程序查询方法;一起,还有4种隶属作业方法,即完毕中止、读状况、中止恳求触发和数据缓冲方法。这些作业方法可以经过初始化指令字寄存器来完结。选用全嵌套方法时,芯片初始化后不用设置操作指令字。中止恳求优先级是固定的:0级最高;7级最低。承受的8个中止恳求信号为边缘触发。设定0级恳求对应中止号为8,直至7级恳求中止号为0FH。单片作业时,实际运用020H和021H两个端口。经过中止优先级分析器选中的当时恳求的中止优先级。其相应的中止服务寄存器ISR位被置1,一向坚持到中止服务程序在回来前发中止完毕指令停止。在ISR置位期间,制止同级或较初级的中止呼应,敞开较高档的中止恳求。

(4)CPLD的编程 嵌入式体系都有灵敏性的要求。因而,本体系选用了Lattice ispLSI系列产品,以习惯不断扩展或开发新的产品以及1个硬件平台上多个种类的完结。运用可编程逻辑器材CPLD,有利于在体系规划和现场运转后对体系进行修正、调试、晋级等。Lattice是带有在体系可编程(ISP)功用的可编程逻辑器材,即不需要从头修正PCB即可修正原有规划。

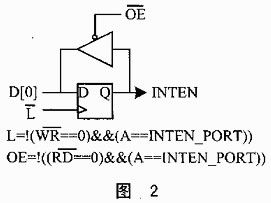

①在CPLD中规划1位寄存器INTEN原理图如图2所示。地址总线A对应INTEN的口地址,数据线D[0]对应INTEN的数据,数据在L的上升沿确定。

②在CPLD中规划一个8位状况机。状况机由XCLK驱动,XCLK经过分频生成100kHz时钟,即Δt=10μs。

3 规划设想

在CPLD中做1个1位寄存器Reg,称为INTEN中止答应,由1个8位状况机依据16C554的中止恳求线发生的INTREQ及INTEN状况来终究生成DLY_IRQ。

①INTREQ为n个中止的或;

②CPU对INTEN只写,操作过程分3步。

第1步,中止装置后设置INTEN=1。

第2步,进入中止服务程序后CPU设置INTEN=0。

第3步,退出中止服务程序的最终指令。

outportb(0x20,0x20);

outportb(INTEN_PORT,0x01);//INTEN_PORT为INTEN的口地址

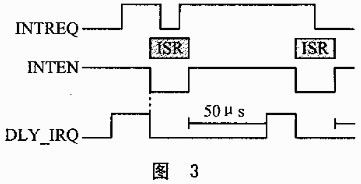

③中止呼应的时序如图3所示。 在ISR置位期间,有中止恳求INTREQ发生时,此刻假如触发了中止,则会使前次中止服务无法完结,因而形成中止丢掉。因而,在ISR装备期间,将中止答应INTEN设置为0,避免其它中止恳求触发中止,并用INTREQ锁存未被呼应的中止恳求。退出中止服务后,得中止答应INTEN设置为1,保证其它中止恳求可以被呼应,并推迟50μs,以保证此次中止服务彻底退出。

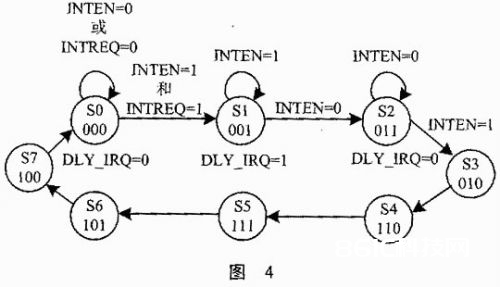

④中止操控寄存器的状况图(描绘8位状况机的转化)如图4所示。 在退出中止时,将INTEN设置为1,从状况S3转化到状况S0。时刻上推迟了5Δt=50μs,保证当时中止彻底退出。INTREQ锁存中止恳求,以保证下一中止能取得呼应。

4 软件规划

在规划中止服务程序时,要注意中止服务程序有必要具有自我维护才能,并能访问到一切当时段地址和仓库指针;接纳中止向量前要关中止;在中止程序入口处要当即开中止;以答应较高档的中止发生;中止程序履行IRET指令前,应向中止操控器宣布完毕中止指令EOI。在装置中止时,将INTEN设置为1,在中止服务中轮番查看多个串口,假如有中止服务发生,则将INTEN设置为0;退出中止服务的时分,将INTEN设置为1。

上面根据嵌入式体系的精简特性,提出了一种高效多串口中止源的完结计划;大大节约了资源,保证中止恳求的无漏检测和服务,并有效地处理了多个串口同享同一中止源时所形成的抵触和丢掉等问题。