1 规划摘要

FPGA芯片具有可编程、可重装备、可并行核算的特色。跟着摩尔定律的开展,核算科学现已步入并行化的年代,具有并行处理才干的CPU/GPU随即问世。而FPGA芯片凭仗其并行核算的才干,现已能够轻松将科学核算、逻辑运算、ASIC规划等运用并行化,为了能将该特性普及化,本规划为依据C言语开发的程序开发了一个FPGA的并行核算接口,凡是以C言语规划的程序,均可经过调用本规划的接口,把杂乱的算法、数值处理交给FPGA芯片完结,在不需求程序员学习FPGA常识以及运用FPGA开发工具的前提下,大大地减轻CPU的负荷以及从根本上提高了程序的履行功率,是FPGA并行化运用的一次全新测验。

2 体系原理与技能特色

体系以依据PC机的Windows操作体系为根底,将FPGA芯片作为一个PCI Express总线设备,经过PCI Express总线与PC机的CPU通讯,在Windows下开发该PCI Express设备的C程序驱动,供给函数接口供C程序调用。Windows下的C程序经过该驱动接口向PCI Express总线发送信号,接入PCI Express总线的FPGA芯片收到该信号后,依据信号的内容调用相应的片内模块进行相应的核算,依托其并行化的特色,能够将大多数的算法与数值处理并行化,最终再将核算成果经过PCI Express总线回来给运转于PC机的C程序,然后完结C程序的并行化,此进程相当于运用外围的PCI Express设备为PC机的程序供给并行化的硬件加快服务。

传统的CPU都归于ASIC器材,存在规划进程杂乱,灵活性不高,不行重装备的缺乏,而作为可重构核算的体系结构代表,FPGA在可重装备和并行运算方面具有一起的优势。

体系的技能特色有以下几点:

(1)并行化加快的完结无需运用新的编程言语和编译器;

(2)运用FPGA的可编程特性以及丰厚的IP核资源,可完结多种类型核算的并行化,因而该硬件加快设备可适用于多个场合;

(3)可具有跨操作体系特性。只需开发相应操作体系(如Linux)下的PCI Express设备的驱动,便可在其他操作体系下运用FPGA的加快功用。

(4) PCI Express总线选用串行的全双工传输,供给高速的数据传输率。PCI Express标准从1条通道衔接到32条通道衔接,有十分强的伸缩性,以满意不同体系设备对数据传输带宽不同的需求。例如,PCI Express X1标准支撑双向数据传输,每向数据传输带宽250MB/s,PCI Express X1现已能够满意干流声效芯片、网卡芯片和存储设备对数据传输带宽的需求,而速度更快的PCI Express X16,即16条点对点数据传输通道衔接来替代传统的AGP总线,适合于需求很多杂乱数学核算的运用。PCI Express X16也支撑双向数据传输,每向数据传输带宽高达4GB/s,双向数据传输带宽有8GB/s之多,因而,挑选PCI Express作为传输总线,不会存在体系瓶颈问题。

(5)PCI总线的资源占用状况

(6)用户在编写程序时,只需求include本文所供给的.h文件,便可调用.h头文件中供给的并行核算函数接口,一起将源代码与本文供给的对应C源文件文件一起编译,即可经过调用PCI总线接口驱动来完结所需的核算。

3 体系软件流程

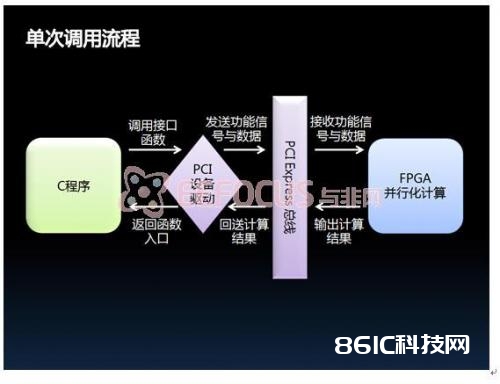

图 1 单次调用接口的软件流程

上图所示为C程序一次调用并行核算接口的进程,C程序与FPGA芯片的通讯经过PCI Express总线来完结。FPGA芯片依据接纳到的信号来判别应该选用哪个独立模块来进行恳求的核算。

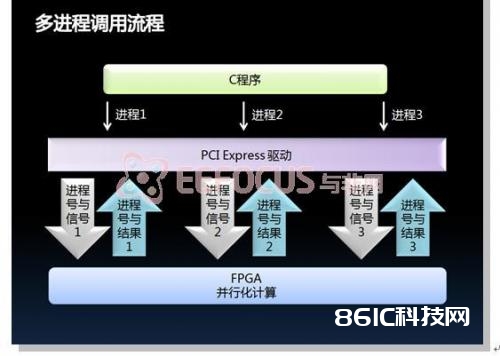

图 2 多进程C程序调用并行接口的流程

上图所示为多进程程序在调用该并行接口时的进程。关键在于在向FPGA芯片发送恳求信息时顺便宣布该恳求的进程ID号,这样在接纳总线发回的数据时才干依据进程号对号接纳。

4 体系结构

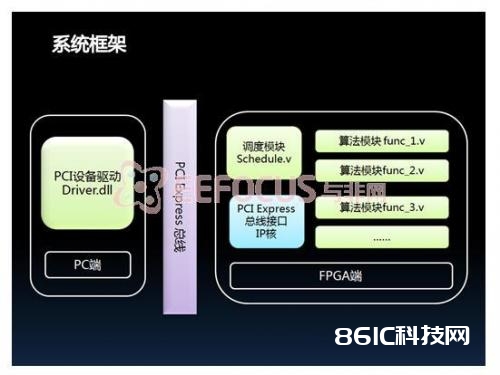

图 3 体系结构

上图所示为体系的组成结构。PC端主要有Windows下的PCI设备驱动(选用WinAPI编写)、PCI Express物理总线;FPGA端主要有PCI Express总线IP核、调度模块以及详细各种算法的Verilog HDL模块。

5 体系功用

5.1 PCI设备驱动程序功用

(1)读写FPGA芯片数据

(2)缓存恳求与成果数据

(3)调度多进程恳求与分配多个进程的核算成果

(4)反常处理

5.2 FPGA调度模块功用

(1)相应PCI总线恳求,判别需求调用哪一个算法模块。

(2)依据恳求类型调度相应的核算模块,并将恳求的数据供给给该模块

(3)接纳核算模块回应的核算成果,再经过PCI Express总线接口的IP核将数据回送给PC

5.3 FPGA PCI Express总线接口IP核功用

(1)经过PCI Express总线读写数据