计算机体系是由许多具有独立功用的模块相互衔接而成的。跟着计算机的不断发展和广泛运用,各生产厂商除了向用户供给整套体系外,还规划和供给各种功用的插件模块,让用户依据自己的需求构成自己的运用体系或扩大原有的体系。这些模块间需求相互通讯,需求有高速、牢靠的信息交流通道,这便是总线。总线使得计算机各模块之间的信号线能够直接相互衔接,提高了信号传输的速度。

VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)是一种硬件描绘言语,在电子规划范畴得到广泛运用,最新版别为IEEE规范的1076-1993版,由IEEE在1993年发布。VHDL首要用于描绘数字体系的结构、行为、功用和接口。本文用VHDL的有限状况机来描绘和仿真计算机总线操控器的逻辑行为。

1 总线在总线操控器的操控下作业

在计算机体系各模块之间的信息通讯过程中,每一时间只能有一组信息在总线上传输。假如有多组信息要传输,只能在总线操控器的操控下,按次第别离传输,这样对每一组信息的传输就构成一个传输周期,这个周期包含恳求分配阶段、寻址阶段、数据交流阶段和吊销阶段。恳求分配阶段由主模块提出总线运用恳求,经总线操控器同意后取得总线运用权;之后主模块把从模块地址放置到地址总线上,即寻址阶段;从模块接收到地址后做好相应的通讯准备作业,并与主模块树立通讯,进行数据交流;数据交流完毕后,主模块告诉总线操控器,并交还总线运用权,即吊销阶段。常用的总线通讯方法有同步通讯方法和异步通讯方法两种。

2 同步通讯方法的有限状况机描绘和仿真

在同步通讯方法里,模块之间的通讯传输周期是固定的。有准确安稳的体系时钟作为传输周期的“标尺”,通讯两边严厉依照时钟标尺进行各种操作,以主模块(如CPU)从从模块(如内存)读取数据为例,总线操控器框图如图1所示。

这种方法下总线的操控状况搬运图如图2所示。

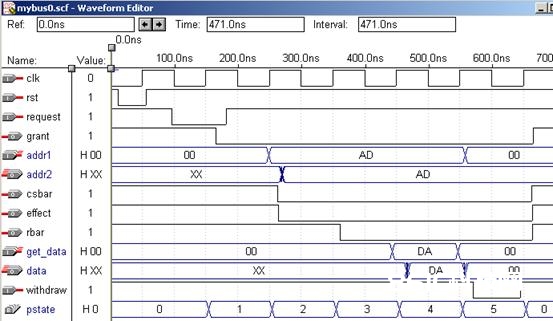

用VHDL进行描绘并在MAX+PLUSII上进行仿真,成果如图3所示:

从图3能够看出,操控器一开始处于状况0(闲暇状况),此刻总线同意操控信号grant、片选信号csbar、地址有用信号effect和读操控信号rbar均处于无效的高电平;一旦有主模块宣布总线恳求,即request信号为低电平,操控器搬运到状况1,总线同意操控信号有用,恳求得到同意,这儿假定主模块只要一个,即不存在多个主模块竞赛运用总线的状况;进入状况2后,主模块宣布地址,这儿假定地址为“AD”,一起置片选信号csbar和地址有用信号effect为有用状况,从模块接收到地址有用信号和片选信号后,依据主模块宣布的地址进行数据准备作业;进入状况3后,主模块宣布读操控信号,即置rbar信号为有用状况;进入状况4后,假定从模块数据准备就绪,并发送到数据总线上,这儿假定数据为“DA”,主模块读取数据;进入状况5后,主模块读数据完毕,宣布吊销信号,即置withdraw信号为有用状况,之后回来状况0,一切操控信号都回来到无效状况;至此,一个数据传输周期完毕。在传输过程中,各个模块的动作严厉依照体系时钟同步进行。

本规划下载到GW48—GK2/PK2 EDA试验开发体系,该体系方针芯片为EP1K100QC208-3,依照结构图No.0进行硬件测验,试验体系供给测验引脚的约束,只测验地址和数据均为4位(测验低4位)的状况,成果如图4所示。

从图4中能够看出,在状况0,首要设置withdraw、request和rst为“1”,顺次对应图中下方3个发光二极管,此刻4个输出操控信号rbar、effect、csbar和grant为“1”,这4个信号按次第组成一个4位二进制数据,该数据通过译码器译码后由数码管显现输出成果,因4个信号均为“1”,故应该显现成果“F”,如图中上面的数码管显现“F”(右边第3个数码管)。第2步,依照图3所示时序设置rst和request信号并由按键3输入一个时钟脉冲,进入状况1,此刻grant信号为“0”,4个输出操控信号组合为“1110”,能够看到图中数码管显现“E”,表明主模块恳求总线被同意。第3步,设置地址信号addr1(低4位)为“1010”,即“A”,如图中数码管下方两个发光二极管所示,并输入一个时钟脉冲,进入状况2,该地址信号由addr2经译码器译码后由数码管显现出来,如图中上面最右边的数码管显现“A”,在该状况中地址有用信号effect和片选信号csbar均为“0”,此状况下主模块宣布地址有用信号和片选信号,4个输出操控信号组合为“1000”,从图中能够看到数码管显现数字“8”。第4步,输入一个时钟脉冲进入状况3,该状况下主模块宣布读操控信号,即置rbar信号为“0”,4个输出操控信号悉数为“0”,如图中数码管显现“0”。第5步,设置数据信号get_data(低4位)为“1101”,即“D”,如图中数码管下方两个发光二极管所示,并输入一个时钟脉冲,进入状况4,该数据信号由data经译码器译码后由数码管显现出来,如图中上面右边第2个数码管显现“d”。第6步,输入一个时钟脉冲,进入状况5,主模块读取数据完毕,并宣布吊销信号,1个数据传输周期完毕;之后假如再输入一个时钟脉冲则回到状况0。