静电可被界说为物质外表累积的静态电荷或静态电荷之间交互作用累积的电荷。电气过应力(EOS)和静电放电(ESD)是电子职业面对的严重应战之一。一般来说,半导体职业中超越三分之一的现场毛病都是由ESD引起的。ESD导致的半导体毛病表现为漏电、短路、焚毁、触摸危害、栅氧缺点、电阻金属接口损坏等。CMOS尺度缩小的优点在于下降功耗,进步速度,但更小的尺度会让较薄的栅氧化层更简略在EOS/ESD状况下遭到损坏。跟着技能进步,尺度不断减小的半导体芯片、较薄的栅氧化层、多个电源、杂乱的芯片以及高速作业的电路,这些都会大幅进步ESD敏感性。栅氧化层厚度的减小意味着较低的电流就或许使其遭到损坏。

ESD猜测是一项单调乏味的作业,因为ESD现象在微观和微观物理层面上都会发生。ESD维护规划是IC规划人员的一大应战。跟着技能不断向深亚微米级展开,为了完结更高的质量规范,CAD流程规划验证中具有增强功用的高稳健性高档猜测模型,是应对ESD所必需的。

ESD损坏一般来历于人工操作、机械臂操作和制作环境中的其它设备,也来历于封装自身累积的电荷。ESD是EOS的子集。可经过两种办法削减ESD引起的IC毛病,一是在制作、运送和运用IC的环境中确保恰当的人员操作和设备接地,以防止发生ESD问题;二是为封装IC的引脚添加维护电路,在呈现ESD应力状况下搬运内部电路的高电流并胁迫高电压。ESD维护电路规划用于在ESD事情中接通,然后胁迫焊盘上的电压。

现场回来器材的毛病剖析能经过显现毛病机制来帮忙规划开发作业。芯片制作商依照工业规范确保产品的ESD质量,不过他们无法控制客户怎么操作,因而要进行片上有用的维护电路集成和测验。

本文将对EOS/ESD做根本介绍,并谈谈电荷搬运机制、ESD测验模型、电气特征和EOS/ESD相关机制,并给出一些毛病剖析与技能的实例。

电荷生成和搬运机制

在介绍EOS/ESD之前,咱们先应了解物体之间的电荷搬运是怎么发生的,电荷搬运机制是什么。电荷生成进程首要有三种:冲突起电(触摸和别离机制)、感应和传导等。

物质外表因为不同物质之间冲突而发生的电荷不平衡就被称为“冲突起电”。电荷的极性和强度取决于物质的冲突电特点、外表粗糙度、施加的压力巨细、温度、张力等。图1给出了两个不同电负性物体X和Y之间电荷搬运的状况。咱们假定物体之间有触摸(冲突),物体X失掉电荷e,而物体Y取得电荷e。因而,物体X相关于物体Y而言带正电。这一现象便是冲突电。

图1:电荷生成机制

让咱们看看日常日子中有哪些冲突电的实例。当人在地板上走,鞋底与地上的触摸和别离就会生成静电。假如人在地毯上走,就或许堆集起数千伏特的电荷,足以发生电火花。经过接地放电,电荷平衡能够得以康复。放电速度极快,只需几纳秒就能完结。一般静电放电电压要到达3kV时人体才会有所感觉。ESD事情一般都会让人感到细微的电击。不过,假如平等的ESD压力注入设备,就或许对设备构成危害。

环境空气中相对较低的湿度也会添加放电时的电压,因为其进步了绝缘物质坚持电荷的才能,并且因为空气传导性下降而导致堆集的电荷难以逐步散失。开车时,驾驶员、乘客的衣服与轿车皮制或塑料内饰的冲突也会堆集起电荷。堆集的电荷在触摸金属车身时或许发生电火花。

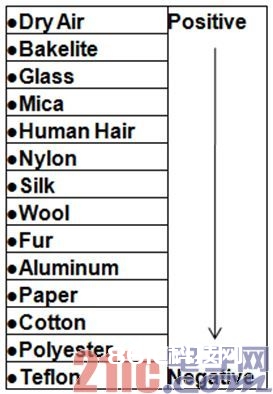

表1:冲突电物质的分类

还有一个冲突起电的实例便是当IC在运送进程中滑动时,因为IC引线和电子管之间冲突而发生的电子管静电。在正常的一天中,人领会发生巨大的静电。表1依据物质的冲突电特点将一些物质进行了分类。

除了冲突电之外,经过感应和传导也能在物质中生成静电电荷。带电物质在环境中发生静电场,如有导电物质进入静电场,则会因感应发生内部电荷散布。图2给出了未带电物体B挨近带电物体A的状况,物体B会得到散布电荷。近端为负电荷,而远端为正电荷。ESD充电器材模型(CDM)则依据静电感应。

图2:经过感应生成电荷

当两个具有不同电势的带电物体互相物理触摸时,电荷会从较高电势物体传递到较低电势物体,直到二者电势相同。这种机制便是传导。

物质的分类

广义地说,物质依据不同的ESD处理类别可分为绝缘体(ρ>1012Ω/□(每平方面积上的欧姆值))、慢电荷耗散性防静电(109ρ1012Ω/□)、电荷耗散性防静电(106ρ109Ω/□)以及导电(ρ106Ω/□)物质。防静电物质能反抗冲突电,因而在制作和安装环境中防静电和耗散性物质可用来约束电荷累积。

电气过应力(EOS)

EOS是用来描绘当IC遭受超出器材数据表规范约束的电流或电压影响时或许呈现的热损坏。EOS事情会构成IC功用下降或永久性功用毛病。EOS比ESD的进程要慢得多,但相关能量却很高。热损坏是EOS事情期间生成过多热量构成的成果。EOS事情的高电流会在低电阻途径中生成部分高温。高温会构成栅氧化层、互联、金属焚毁等器材物质损坏。一般说来,EOS和ESD被归为一种毛病机制,即“ESD和EOS毛病”。这是因为EOS和ESD毛病方法很像。ESD和EOS的过应力事情很像,但电流或电压以及时刻过应力条件不同。ESD电压很高(>500V),峰值电流一般(~1A到10A),发生时刻很短。EOS的电压较低(100V),峰值电流很高(>10A),发生时刻较长。如闩锁效应长时刻持续,也会构成EOS损坏。

静电放电(ESD)

ESD是指两个具有不同静电电势物体之间经过直触摸摸或感应电场而发生瞬态静电放电。ESD是静电带电物体经过IC静电放电导致较大电流和能耗的成果,然后损坏IC。任何物质外表的电荷一般是中性的,如传递能量,就会呈现电荷不平衡。

导体因为导电外表较高的电子流动性不太简略带电,因而会呈现电荷重组并坚持中性外表。另一方面,冲突很简略让绝缘体带电。传递能量到不导电物质上就会堆集很多部分电荷,终究经过外部途径进行放电。静电的首要来历便是绝缘体,如塑料外表、绝缘鞋、木材、泡沫包装等。因为绝缘体的电荷散布不均匀,因而其生成的电压会十分高(kV)。

此外,IC的ESD损坏也是热现象。部分体积快速发生很多热,很难消除,这就构成金属互联烧坏、聚酯损坏、栅氧化层损坏、触摸损坏、结点损坏等IC损坏。

当人走在合成树脂地板上,生成的电压或许高达20kV。枯燥空气中冲突尼龙和聚酯物质发生的电压可高达25kV。假如此人触摸接地物体,电荷会在极短时刻(1到100纳秒)内从人体移到该物体上,放电时刻和电流详细取决于时刻常数。

放电电流约为1到10A。从工厂到现场运用进程中随时都有或许呈现电子设备的静电损坏。半导体设备的规划需考虑ESD维护问题,要能在短时刻内接受高电流。举例来说,假如设备经过ESD-HBM认证,能接受2kV的规范电压,那么该设备就能在10纳秒的上升时刻内接受1.3A的电流,或许在150纳秒的下降时刻内接受1.3A电流。不过,该产品不能在几毫秒内接受100mA。假如该产品遭受较弱的ESD脉冲而部分损坏,或许仍能持续作业,并足以经过满意数据表规范要求的量产ATE测验。这个缺点会跟着时刻的推移而延伸,几个小时后就会构成产品毛病。这种缺点便是潜在缺点,由此构成的毛病为潜在ESD毛病。潜在缺点难以检测,特别在器材现已安装到制品中的状况下更是如此。

有许多要素都可导致EOS和静电放电(ESD/EOS)发生,比如欠佳的片上维护电路规划与布局、技能、出产东西、制作和安装工艺、运送以及规划人员电路板规划等现场运用等。规划人员在运用进程中,或许会因瞬变、接地不正确、电源电压与地上之间的低电阻途径、电源引脚或地上短路、内部电路受损等原因呈现ESD/EOS现象。关于IC而言,假如其所在环境超出数据表规范,则终究会发生毛病。假如IC在数据表规范规模内作业,则其组件的内部条件是不会发生EOS损坏的,因而,EOS损坏只要在条件反常时才会呈现。测验和处理设备时假如接地不正确就会堆集静电荷,这些电荷在触摸IC之后,当即经过IC传递。

ESD测验模型

尽管半导体器材包含EOS维护电路,可是为了确保其满意JEDEC规范规则的有用性和牢靠性要求,有必要展开ESD测验来查看零部件是否合格。ESD测验首要有3个测验模型:HBM(人体模型)、CDM(充电器材模型)与MM(机器模型)。HBM仿真人体放电发生的ESD。人体被认为是首要的ESD来历,一般选用HBM描绘ESD事情。CDM仿真带电器材触摸导电物质后放电。MM则仿真物体向组件放电。该物体可所以任何东西,也可所以出产设备。下文会对各个测验模型进行详细描绘。

人体模型(HBM)

人在走路时会发生电,但这些电都会进入地上。每走一步都会堆集电荷,咱们能够选用下列方程式来表明该电荷:ΔV/Δt = n Δq/C,其间,n表明每秒的脚步数,C表明人体电容。请想象一下绝缘地上上的常见景象,成果表明,每走一步ΔV就会添加300V,10秒内到达3kV左右(注:部分电荷走漏)。

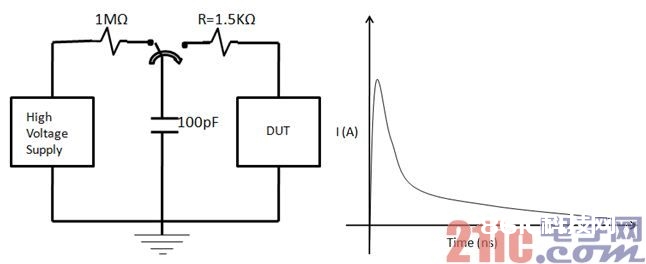

在HBM测验中,咱们选用了简略的串联RC网络,如图3所示,用来仿真人体放电。咱们运用1MΩ的电阻给100pF电容器充电,然后运用1.5kΩ电阻对其进行放电。大部分HBM事情都是损坏性的,并且上升时刻快。因而,选用快速上升时刻脉冲能够愈加精确地仿真HBM放电事情。

图3:ESD–HBM测验设置与电流波形图

所发生的热量取决于电容、DUT电阻以及ESD脉冲的峰值电压。所发生的热量会引发金属线熔化等热损坏。在HBM测验中,不管IC呈现哪种方法的毛病方法,栅氧化层、导电棒与结点一般都会损坏。图3给出了测验设置和电流波形图的特征。首要串联1MΩ电阻和100pF电容器,然后施加高电压。电容器充满电后,经过1.5kΩ电阻放电至DUT引脚。

充电器材模型(CDM)

CDM可仿真HBM测验无法仿真的现场毛病损坏。CDM仿真的景象是:运用冲突起电效应直接给器材充电,或许经过静电感应间接给器材充电(静电荷存储于零部件本体之中,经过外部地上放电)。

图4:ESD–CDM测验设置与电流波形图

本测验旨在仿真出产环境下的各种景象,比如处理机械器材等等,器材沿运送管道或测验处理机滑下,堆集电荷,随后该电荷又被放电至地上。CDM ESD测验和典型的电流波形图参见图4。外部地上触摸被充电器材的DUT引脚之后,器材则将所存储的电荷放电至外部地上。在CDM测验中,器材在测验固定装置上,反面一直朝上,如图4所示。

CDM电流高于HBM,因为途径中并没有限流电阻器约束放电。关于500V的测验电压而言,电流波形上升时刻一般在400皮秒左右,峰值电流为6A左右,峰值电流持续时刻为1.5至2纳秒。关于1000V的测验电压而言,峰值电流强度为12A。

机器模型(MM)

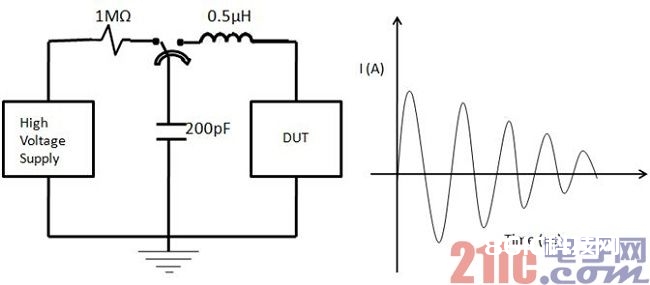

机器模型又被称为0欧模型,旨在仿真经过器材向地上放电的机器。MM测验中,毛病方法相似于HBM测验。在测验设置中,高压(HV)电源与电阻串联,给电容器充电,运用开关将电容与高压电源堵截,然后将电容器衔接至电感器进行放电。电感器发生振荡电流波形。MM所选用的根本测验电路和HBM相同,但R=0Ω、C=200pF,如图5所示。充电时,200pF的电容器充任金属处理器等导电性物体,运用1MΩ电阻和0.5μH电感器进行放电。MM测验的运用没有HBM测验遍及。MM电流特征波形由正向正弦波峰和负向正弦波峰组成,这两个波峰均呈指数衰变。

图5:ESD–MM测验设置与电流波形图

HBM、CDM与MM的比照

HBM与MM的上升时刻(即10秒左右)和总持续时刻相似,因而,它们的焦耳热效应适当,毛病机制也因而相似。MM测验中,毛病特征和放电进程与HBM测验大体相同。因而,HBM测验能够确保MM的ESD稳健性。一般而言,MM ESD的应力水平比HBM ESD低10倍左右。HBM维护电压一般是2kV左右,而MM则为200V左右,CDM为500V左右。CDM与HBM和MM天壤之别,因而,CDM与它们无任何相关。现在,遍及选用CDM和HBM测验ESD维护电路。图6给出了HBM、MM和CDM的电流波形。CDM波形对应最短的已知ESD事情,上升时刻为400皮秒,总持续时刻为2秒左右。

图6:HBM、CDM与MM的电流波形图

ESD抗扰度分类

咱们经过上文现已了解了不同模型的ESD测验过程与设置。器材的ESD活络度度可界说为:该器材能够经过的最高ESD测验电压和让其发生毛病的最低ESD测验电压。每个模型都有自己的分类,以便依照ESD活络度对器材进行分类。表2、3、4列出了HBM、CDM与MM的分类状况。

表2:HBM的ESD抗扰度分类

表3:CDM的ESD抗扰度分类

表4:MM静电放电扰度分类

遭受ESD应力的%&&&&&%有着显着的毛病特征。高电流会消融半导体结构的不同区域(ESD-HBM),而高电场则会损坏电介质(ESD-CDM)。ESD引发的最常见毛病方法便是输入/输出引脚处漏电或电阻短路,经过测验台或ATE测验检测现场返修的产品就能发现这种状况。其它毛病方法包含高封闭电流(IDDS)、供电电流(IDD)和无输出等敞开引脚。开路和短路可经过I-V曲线盯梢测验台观察到。内部电路损坏检测则需要高档毛病剖析技能。在本节中,咱们将详细介绍ESD/EOS损坏器材的电气和物理剖析。

HBM和CDM代表不同的EOS类型。EOS和ESD能够多种方法损坏半导体器材。大多数EOS和ESD构成的毛病都跟以下毛病机制有关:

● 热损坏或焚烧金属化

● 氧化物或电介质击穿

● 触摸损坏或结点损坏

热损坏

热损坏是一种EOS和ESD机制。因为EOS-ESD事情中生成很多热量,金属导体或电阻接头熔化。作为保险丝的金属线熔化变成开路。EOS、ESD-HBM事情中会观察到金属熔化。不过,假如导体膜较厚,金属会部分熔化,或许影响器材的功用。假如金属线电阻为R,电流为IESD,那么发生的功耗为P=I2ESD*R。当部分热量构成温度上升到金属线的熔点时,就会呈现金属熔化。以下给出了一些EOS和ESD-HBM的实例。

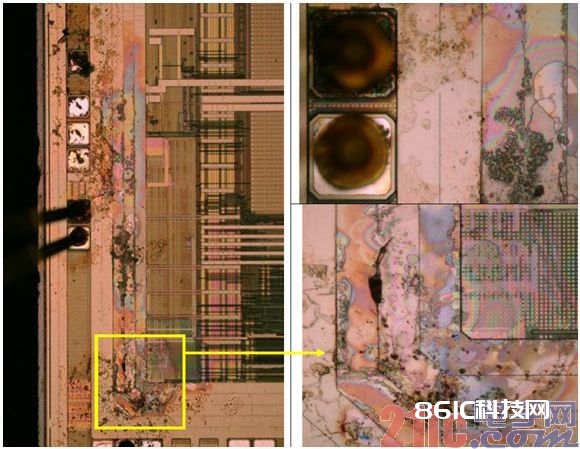

在图7中,器材的引脚至引脚I/V曲线没呈现短路、开路等不正常状况,但取下后SEM呈现焚烧金属化。

图7:EOS构成的焚烧金属化图示

氧化物或电介质击穿

氧化物击穿可分为软击穿或硬击穿。软击穿是指电介质上的高电阻电流途径,而硬击穿是指电解质层上的高传导性途径。在氧化物软击穿中,器材仍能杰出作业,晶体管功用不会发生很大改变。这时会发现漏电状况比正常器材略高,但仍或许在数据表约束规模以内。在氧化物硬击穿中,器材无法作业,从栅极到通道构成电流途径,晶体管被损坏。

栅氧化层损坏是ESD事情中最常见的。栅氧化层击穿取决于氧化物的厚度、偏置电压、氧化物资料的击穿电压、氧化物膜的均匀度和粗糙度等。如氧化物膜有尖利边际,那么感应电场会高度集中在边际上,很或许被击穿。

假定氧化物层厚度为100A0而氧化物层上的电压为3.3V,那么氧化物层上的均匀电场核算如下:E=V/Tox

氧化物或电介质击穿

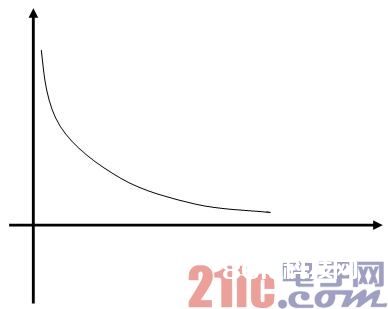

电介质资料二氧化硅的击穿电场为11x106V/cm。如氧化物厚度减为50A0,E=6.6x106V/cm且电介质间的电场添加,就会趋近于击穿。如V为常量不变,E.Tox=常量,这是一个双曲线方程式(XY=C)。图8给出了电场和氧化物厚度的曲线。

图8:电场和氧化物厚度

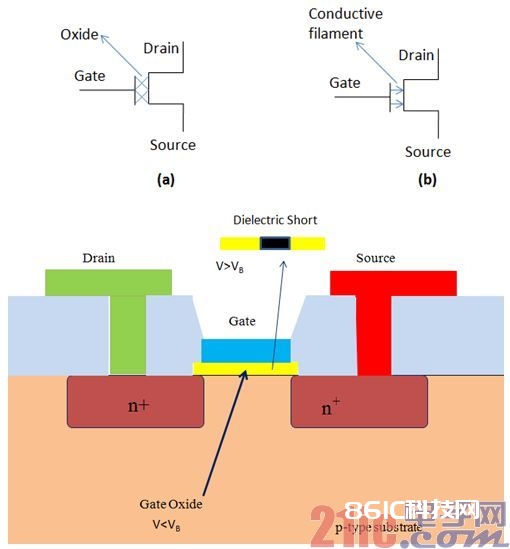

图9:(a)ESD脉冲前的栅氧化层、(b)遭到损坏的氧化物构成的细丝和(c)V>VB电介质短路等原理图

氧化物击穿有以下机制:氧化物层上的电压超越氧化物(电介质)的击穿电压(V>VB),这样栅氧化层会被击穿,氧化物层上构成较低电阻或传导途径。因为电流流过途径的电阻减小(氧化物或电介质击穿),会呈现电介质的部分升温。因为部分温度较高,传导方位熔化,构成细丝,然后导致电介质上的金属层短路,如图9所示。氧化物击穿是CDM的首要击穿机制。

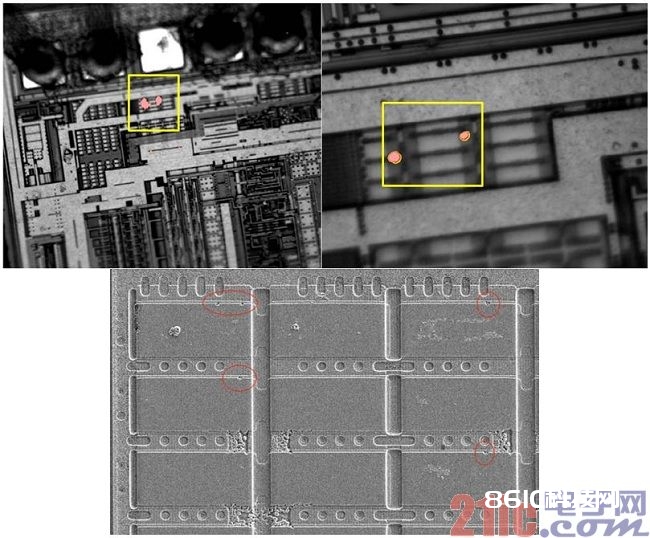

图10:栅氧化层决裂

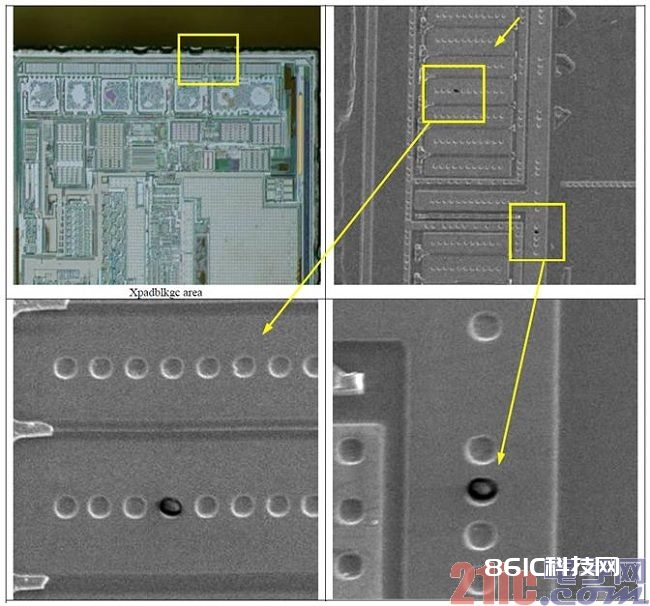

图10给出了ESD-CDM事情中呈现氧化物决裂的状况。在毛病部件中,测验台没有观察到输出。在电阻隔状况下,振荡器电路的参阅输入引脚处观察到高漏电。振荡器模块的参阅输入引脚%&&&&&%处也检测到热门。

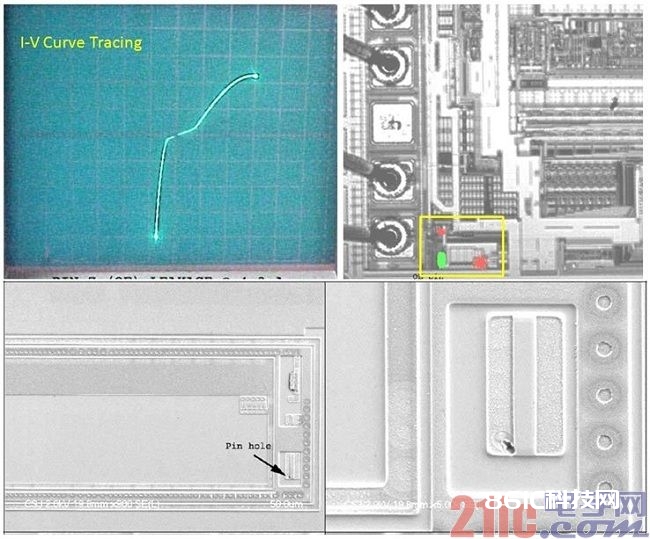

图11显现了没有观察到输出的晶体振荡器的ESD损坏状况。测验台(I-V曲线盯梢)显现OE(输出启用)引脚处有4.3mA的漏电。毛病点阻隔用Hamamatsu emission/OBIRCH显微镜查看完结,将问题部分化。在毛病引脚的输入电路上检测到热门。随后选用等离子/化学蚀刻进行物理剖析发现emission microcopy辨认的热门区域存在引脚孔。

图11:I-V曲线盯梢、热门和引脚孔的图示

触摸毛刺或结点损坏

触摸毛刺或结点损坏是指p-n结点因ESD事情构成的焦耳热效应损坏。当芯片加热后,共价键被损坏并生成电荷载体,而芯片的电阻率和热传导性跟着温度升高而下降。

图12:触摸损坏的SEM图

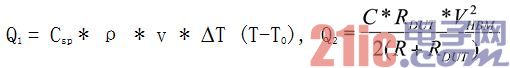

ESD脉冲作为一个电流源。当ESD脉冲忽然施加到芯片上时,会加热不均匀。部分区域在绝热条件下加热,较高电流提高结点温度,并超越芯片的熔点,然后构成结点熔化。图12显现ESD构成的触摸损坏。ESD发生的能耗引起触摸毛刺或结点损坏,其核算如下:

在绝热条件下,ESD事情发生的能量等于结点吸收的能量:Q1=Q2

其间,

假定Q1=Q2

Csp=详细热容量,ρ=密度,T0=初始温度

假如T≥Tm(熔点),那么就会呈现结点熔化。

Wunsch Bell模型选用以下热扩散方程式,这是描绘结点击穿的最常用模型。在此模型中,结点击穿现象由脉冲宽度和器材施加的功率密度决议。

其间,P=以瓦特为单位的毛病功耗,A=以平方厘米为单位的面积,Cp=以J/gcm-K为单位的热容量,ρ=以g/cm3为单位的密度,κ=以W/cm-K为单位的热传导,t=矩形脉冲宽度,Tm=结点熔化温度,而T0=初始温度。

以上方程式说明晰温度、ESD脉冲电压、毛病功率和资料熔点之间的联系。