摘要:跟着高清影音年代的到来,新的高清多媒体接口技能也渐趋老练。本文研讨了高清多媒体接口的编码和解码功用,并选用硬件描绘言语完成高清多媒体接口规范界说的编解码功用。首要对高清多媒体接口的全体信道传输进程进行了剖析和分化,并论述了三个数据周期传输时刻及其解码办法的不同。在此根底上对编解码功用进行了模块区分,选用分层及模块复用至顶向下的规划办法。终究经过NC—Verilog仿真东西仿真验证代码功用的正确性。

关键词:高清多媒体接口;编码;解码;至顶向下;仿真

0 导言

数字影音技能开展一日千里,多媒体视听范畴正在进行着一场革新,跟着生活水平的进步,一般影音己不能满意人们的需求,寻求高清晰画质,立体感音质,现已成为新一代人寻求时髦的一种诠释。

在曩昔适当长的一段时刻,CRT(Cathode Ray Tube)为代表的模仿显现设备主导了整个显现设备商场。跟着高清视频格局(720p/1080i/1080p)的承认,液晶电视、等离子电视等大尺度数字化平板显现设备的创造和遍及,传统模仿接口易受电磁搅扰、传输速率低、带宽小、传输损耗大等缺陷现已不能满意海量数据流传输等需求;一起,影视等职业对版权认识越来越注重,数据传输的加密变得益发重要,传输更快更安全的全数字化接口替代模仿接口成为必然趋势。所以第一个职业支撑的、无紧缩的、全数字的音视频接口 —HDMI诞生了。

HDMI的全称是“High Definition Multimedia Interface高清多媒体接口”。2002年4月,来自电子电器职业的7家公司——日立、松下、飞利浦、Silicon Image、索尼、汤姆逊、东芝一起组建了HDMI高清多媒体接口安排HDMI founders(HDMI论坛),HDMI founders在2002年12月9号正式发布HDMI1.0版规范,标志着HDMI技能正式进入历史舞台。跟着HDMI规范自身的开展,1.3a版别和2.0等后续版别也连续推出,不只功用愈加强壮,兼容性也愈加超卓。

在HDMI规范拟定之初,承继了DVI规范中相对老练且较简单完成的部分技能规范。整个传输原理依然是依据Silicon Image公司的TMDS(Transition Minimized Differential Sienaling)编码技能。

HDMI具有体积小、抗搅扰强、兼容性好、智能衔接、单线缆一起传输无紧缩音视频等优势。因而,它已被广泛地应用到DVD、机顶盒等设备中,HDMI正在成为高清年代遍及率最高、用处最广泛的数字接口。

1 HDMI概述

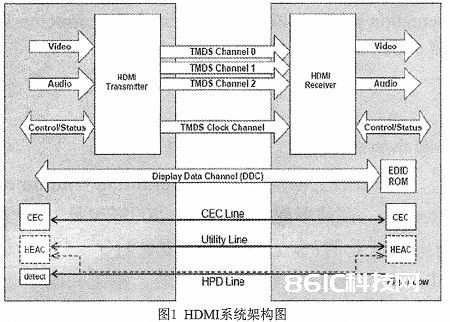

HDMI体系架构由信源端和接纳端组成。如图1所示,HDMI供给四个独立的TMDS(Transition Minimized Differential Signaling)通讯通道:三个数据信道和一个时钟信道,这些信道首要用于传递视频、音频和辅佐数据。别的,HDMI供给一个VESADDC(Video Electronics Standards Association)(Display Data Channel)信道。DDC是用于装备和在一个独自的信源端和一个独自的接纳端交流状况,读取接纳端的E-EDID数据结构。CEC(Consumer Electronics Control)是一个可选信道,可选择在用户的各种不同的音视频产品中,为高端用户供给高水平的操控功用。可选择的HDMI以太网和音频回来(HEAC),在衔接的设备中供给以太网兼容的网络数据和一个和TMDS相对方向的音频回来信道。

音频,视频和辅佐数据都是在三个TMDS数据信道中彼此交织传输。TMDS时钟,即视频像素速率传输时钟,在TMDS时钟信道中传输,它被接纳端三个 TMDS信道作为一个频率参阅,用于对三个TMDS数据信道的数据恢复。在信源端,TMDS编码将每个TMDS数据的8bits数据转换成10bits的 DC-balanced数据,10bits的DC-balanced数据将以每个TMDS时钟周期串行地在差分线对上进行传输。

视频数据像素时钟的TMDS时钟上传递默认值为24位色深,视频数据还兼容30,36,48位像素的数据。更高的色深运用需求相应的更高的TMDS时钟率。视频格局TMDS时钟率低于25M能够运用像素复用发送的战略来进行传输。视频像素支撑多种编码格局,能够是 RGB,YCbCr4:4:4,YCbCr4:2:2格局编码。

TMDS信道传输音频和辅佐数据中,HDMI的信源端需求采取用包的格局来确保传输。为了确保音频和操控信号的高保真度,音频和辅佐数据数据需求BCH纠错码的编码办法,且采取了一种10bits削减过错编码的特别编码办法。根本的音频传输功用简直包含一切的一般的立体声音频,在采样频率别离为 32KHz,44.1KHz和48KHz情况下的IEC60958L—PCM音频流。HDMI还能够传输采样频率高达192KHz,选用3到8个音频通道的音频流。HDMI相同能够传输采样频率高达24.576MHz的IEC61937紧缩音频。HDMI相同能够传输2—8通道的OneBit音频或者是一种被称为DST的紧缩的One Bit音频。

2 HDMI编码规划

本规划是依据HDMI 1.4版别的编解码规划。首要分为两个大模块规划,即HDMI TX编码模块和HDMI RX解码模块。TX编码模块首要完成把视频、音频数据经过编码传输给Rx解码模块。RX解码模块首要把视频、音频数据解码后传输给外置设备。

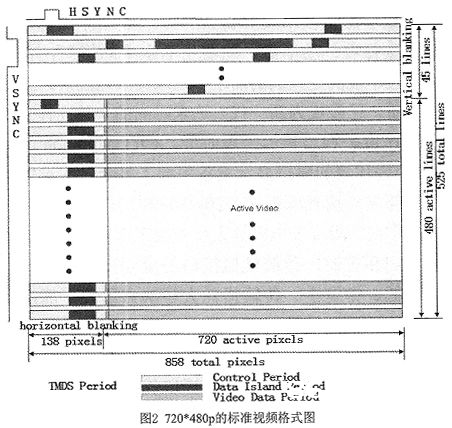

如图2所示,HDMI有三种处理数据的操作方式:视频数据周期,数据岛周期,操控周期。在视频数据周期,传输每一个有用的视频像素行。在数据岛周期中,音频和辅佐数据运用一系列数据包来传输。在音频和视频周期的两个非操控周期之间要刺进操控周期。

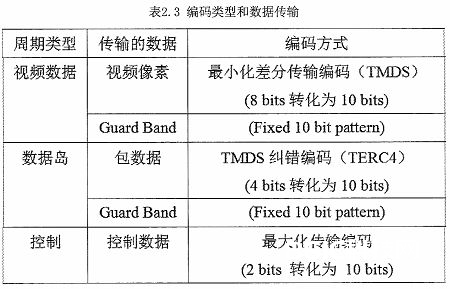

视频数据周期选用最小化差分传输编码(TMDS)的编码办法,对每个8bits传输信道进行编码,三个传输信道共24bits数据。

数据岛周期选用TMDS纠错编码(TERC4)的编码办法,每个4bits传输信道进行编码,三个传输信道共12bits数据。

操控周期选用最大化传输编码的编码办法,对每个2bits传输信道进行编码,三个传输信道共6bits。这6bits数据包含HSYNC、VSYNC、CTL0、CTL1、CTL2、CTL3。在每个操控周期的结尾有一个报文头,运用CTLx bits数据组成的preamble,指示下一个数据周期是视频周期仍是数据岛周期。

每一个数据岛周期起始于前导维护带(Leading Guard Band),完毕于后置维护带(Training Guard Band);而视频数据周期只始于前导维护带,没有后置维护带。维护鸿沟两个特别字符组成,规划方针是供给从操控周期到数据周期或从数据周期向操控周期转化的鲁棒决议方案。

下表2.3展现在数据传输中每种操作方式的编码类型。

2. 1 编码器TX模块

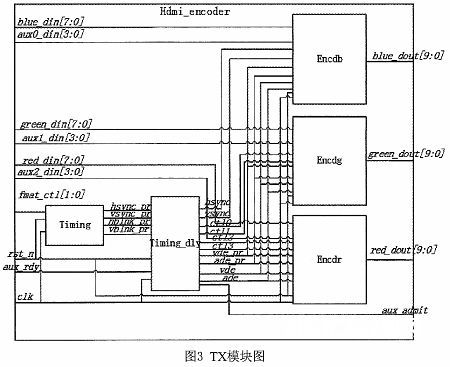

TX(信源端)发射模块,包含时钟模块(由Timing和Timing_dly两个模块组成)、以及编码模块。时钟模块首要为视频音频交织相传发生时钟,编码模块完成对视频音频数据编码传输。

2. 1.1 时钟模块

(1)Timing模块

Timing模块是HDMI编码器的根底,它发生720*480p、1280*720p、1920*1080i等视频格局的行信号hsync_pr、场信号vsync_pr、行无效信号hblnk_pr和场无效信号vblnk_pr。如图2所示,hsync_pr、vsync_pr别离为HSYNC、 VSYNC;hblnk_pr为每行前138 pixels置高位,vblnk_pr为每帧前42行和后3行共45行置高位(注:详细界说以CEA-861-D中规则的720*480p的规范视频格局为准)。

(2)Timing_dly模块

Timing_dly模块是HDMI高速数据传输的中心,依照TMDS通道的视频音频交织传输数据要求,分配视频数据、音频数据和辅佐数据,以及操控数据的传输时刻周期,并为编码模块供给操控信号。

首要端口界说:

hsync_pr、vsync_pr;行信号和场信号。

aux_rdy:当输出是“1”,则外部数据缓存音频数据预备完毕,能够传输音频数据;不然,音频数据未完成打包,停止传输音频数据。

aux_admit:当输出是“1”,则传输音频数据;不然停止承受音频包数据。

ade、vde:别离表明传输音、视频数据标志位,为高时表明进入数据岛或视频数据周期。

2.1.2 encoder模块

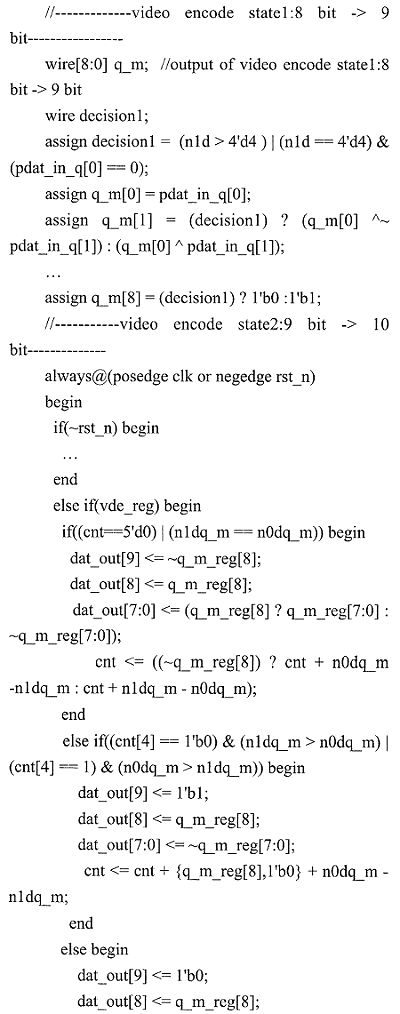

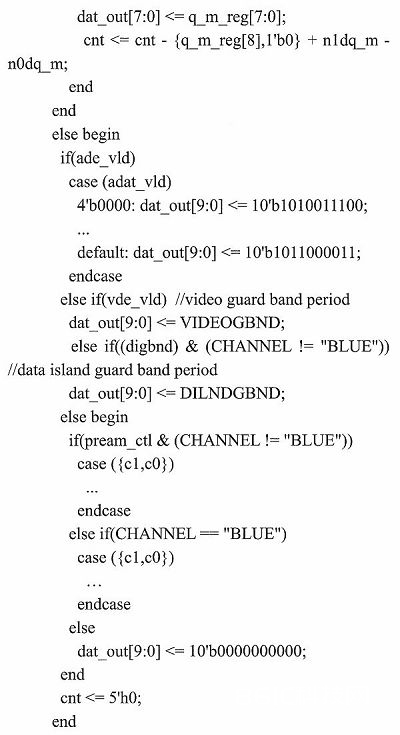

timing模块选用TMDS编码、TERC4编码和最大化传输编码三种编码方式,对视频数据、音频数据包和辅佐数据、操控数据编码传输。

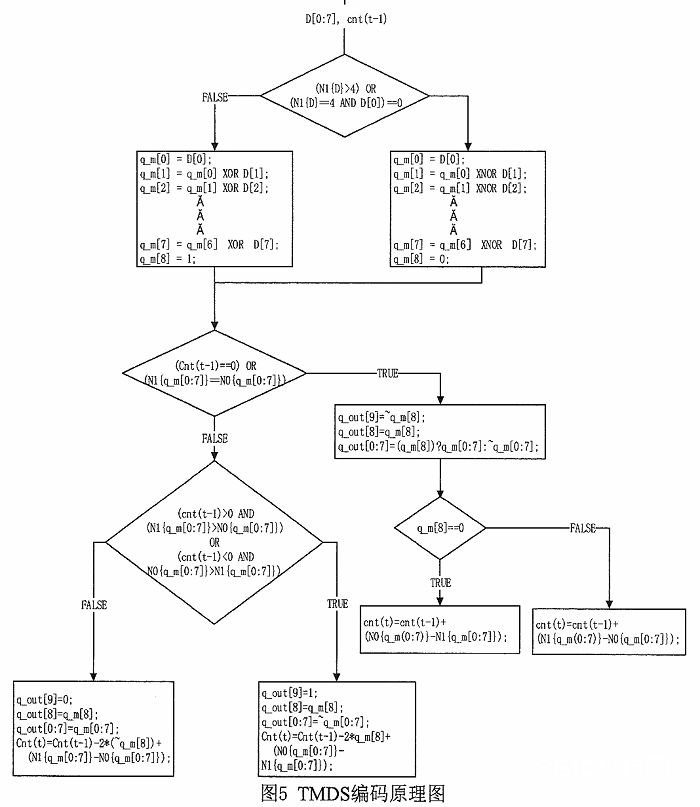

视频像素数据的编码可分为两个阶段:第一个阶段是输入音频的8bits像素数据转换成9bits数据;第二阶段是把9bit数据转换成TMDS传输10bits。

完成的TMDS编码算法如图5所示。

D:输入8 bits视频数据。

cnt:核算编码数据中0和1个数的差值。若cnt为正值表明发送1的数量超越0的数量,负值则表明发送0的数量多于1的数量。cnt{t-1}表明相对于输入数据的前一个周期的cnt的值,cnt{t}表明本周期的值。

q_m:第一阶段的9 bits输出数据。

q_out:第二阶段的10 bits输出数据,即编码器输出值。

N1{x}:这个操作符回来参数x中的1的个数。

N0{x}:这个操作符回来参数x中的0的个数部分中心代码如下:

2.2 解码器RX模块

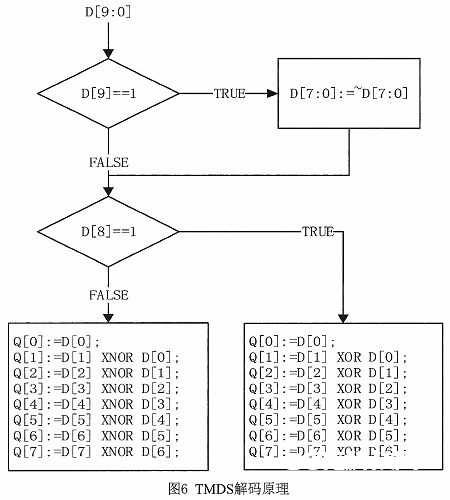

解码器模块较简单完成,只需依据preamble操控位判别接下来传输的数据类型,即音频或视频数据,然后解码即可。解码相同分两个阶段,如图5所示,第一阶段由10bits数据转为9bits数据,第二阶段由9bits数据转为8bits数据。

图6 TMDS解码原理

3 HDMI功用仿真验证

在HDMI功用验证选用分层验证法,依据Spec1.4的编码解码的要求,拟定验证方案,规划各种鼓励,完成近百分之百的覆盖率。本文运用的东西是Cadence NC—Verilog,文中介绍部分验证方案,以及验证的成果。

3.1 时钟模块的功用仿真验证

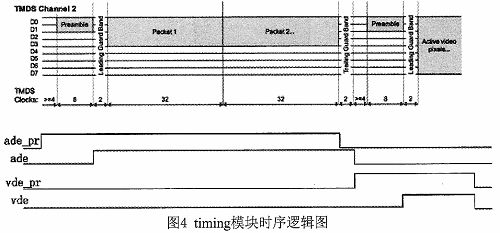

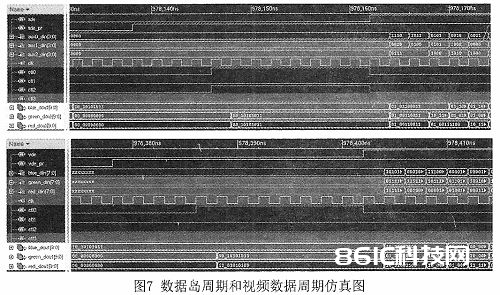

按Spec1.4要求,给定仿真必需鼓励信号,仿真数据岛周期及视频数据周期的每个像素时钟的功用散布是否契合Spec1.4的要求。比方验证ctl[3:0]的正确性,如图4所示,在3个blanking、8个preamble、2个leading guard band的时钟周期之后,进入下一个状况,ctl[3:0]的值与状况所表明的值比照便可验证。

在验证数据岛周期:在ade_pr置高位后,经过4个blanking+8个preamble+2个leading guard band。packet传输完毕后置低位。ade置高位进入data island period,再经过2个leading guard band+N个32位的packets+trialing guard band。trialing guard band后置低位。在8个preamble时,ctl[3:0]=4’b0101。

在验证视频数据周期时:vde_pr置高位后,经过4个blanking+8个preamble+2个leading guard band。video data传输完毕后置低位。vde置高位进入video data period,再经过2个leading guard band+active video pixels。video data传输完后置低位。在8个preamble时,ctl[3:0]=4’b0001。

图7数据岛周期和视频数据周期仿真图

3.2 HDMI模块仿真

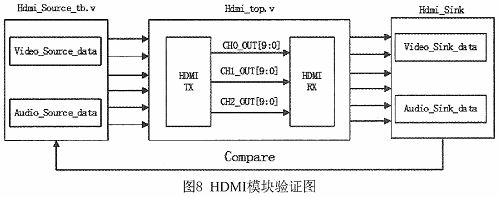

把时钟模块和encoder模块整组成TX模块,其间encoder模块别离实例为Encdr、Encdg、Encdb三个信道的编码模块。将TX和RX模块,即hdmi_encoder和hdmi_decoder,组合在一起仿真。

如图8所示,输入的音频、视频数据用random函数随机发生,且在固定的时刻周期输入,将输出与输入比照,得出HDMI整个编解码模块是否正确。

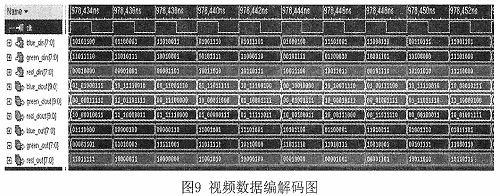

如图9所示,第一组为7bits视频数据输入,第二组为编码后的10bits视频数据输出,第三组为解码后的7bits视频数据输出。视频数据编码需求三个时钟,解码需求两个时钟,所以每距离五个时钟输入7bits数据等于输出的7bits数据,即从编码到解码总共需求五个时钟。

4 定论

进入21世纪,在带宽、音频、传输安全等方面具有优越性的HDMI的呈现,满意了数字高清年代海量数据流传输的需求。本规划运用 verilog HDL完成HDMI编码及解码功用,经过写仿真测验鼓励及运用NC—Verilog东西仿真代码逻辑的正确性。从子模块、模块、体系仿真验证自底向上的办法来进行,终究依据仿真验证成果承认完成编解码功用。非常感谢芯珠微电子林泉工程师及梁文锋、黎伟莲、洪传练、杨家昌等搭档的协助,本规划的不足之处将在后续工作中改善。