摘要:文中介绍了ATMEL公司的高性能AVR单片机ATmega103的首要性能特色,给出了ATmega103在FH跳频体系数字信号处理模块中的运用办法,详细介绍了片内同步串口SPI的运用技巧,一起给出了SPI的通讯运用程序。 要害词:单片机;跳频;SPI;数字信号处理;ATmega103 ATmega103单片机是ATMEL公司推出的精简指令集(RISC)AVR(ADVANCE RISC)系列单片机产品,这是一种增强型RISC结构,选用了CMOS技能的8位微操控器该结构能有用支撑高档言语以及密布度极大的汇编器代码程序。 跳频体系(FH)是指载波频率按某种跳频图画(跳频序列)在很宽的频带规模内跳变的通讯体系,因为该体系具有抗干扰、抗多径和抗式微性等才能,故在军用和民用范畴都得到了广泛的运用。本体系计划中,信号处理模块首要完结跳频形式(FH)下有关数字信号的处理,包含话音编解码、话音安排及与同步有关的操作等,这些技能现在是跳频体系的要害技能之一。 本文介绍ATmega103单片机的特色及其在FH体系数字信号处理模块中的运用办法,一起详细介绍SPI(Serial Peripheral Interface)的特色和运用。 1 ATmega103单片机概述 ATmega103是依据AVR RISC结构的8-bit低功耗CMOS微处理器,它吸取了PIC系列及8051系列单片机的长处,并作了严重改善,其特色如下: ●供电电压为2.7~6V,主频最高可达12MHz; ●具有120条指令,大多数指令执行时间为单个时钟周期; ●带有128k字节片内可下载的Flash存储器(SPI串行下载1000次寿数)和4k字节的片内RAM以及4k字节的片内EEPROM; ●有32条可编程I/O线、8条输入线和8条输出线; ●具有32个8位通用寄存器; ●内含2个8位定时器和1个16位定时器; ●带有可编程串行UART+SPI接口; ●具有内部中止源和8个外部中止源; ●带有8通道10位A/D转换器、片内模仿比较器以及看门狗等电路; ●可在线编程。

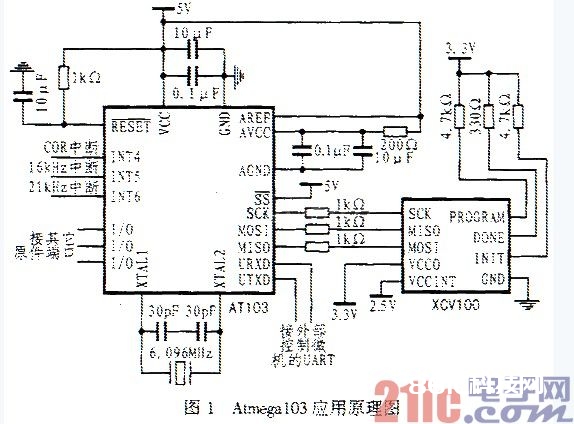

ATmega103因其上述特色使其成为一种适合于多功用、快速,且具有高度灵敏性和高性价比的微操控器。 2 跳频信号处理对单片机的要求 跳频信号处理模块是FH电台的要害部分之一,首要用于完结电台的同步及有关数据处理安排等使命。单片机是该模块的中心,模块的许多功用都是在单片机的直接或直接参加下完结的。归纳考虑,单片机在该模块中的效果大致如下: (1)完结很多数据交流,因为电台在作业时需求接纳或传送很多其它单片机以及模块内部的有关参数数据; (2)完结快速实时处理功用,因为模块对许多信息要求当即处理,例如TOD(Time of Day)信息、话音数据、实时作业频率核算等。 (3)用于数据交流,包含单片机接口、TOD、同步信息、操控状况参数数据接口等。 (4)完结很多运算。一般电台在FH作业方式时,每跳都需求核算TOD、作业频率、接纳或发送数据的重新安排。 (5)经过满意的I/O口来供给多种操控状况线,以供电台及模块内部运用。 (6)经过片内很多数据来存储区存取运算过程中发生的很多中心数据。 3 规划思路 依据电台FH信号处理模块对单片机的要求,假如选用89C5X系列单片机,不光在完结功用上比较困难(如运算速度、I/O口数量等),并且所需的外围扩展电路也有必要添加(如RAM,通讯口等)。而选用ATmega103单片机则能较好地满意规划要求,因而,本规划选用ATmega103单片机来完结信号处理模块的功用。图1所示是其硬件原理图。 此外,在实际运用中,还需留意软件规划。为了便于调试、保护及功用扩展,该体系选用模块化程序规划计划;并且考虑到软件的可靠性,还添加了容错和冗余规划;一起,针对数据接口多的特色,程序中还规划了简明、通用性的接口通讯协议。 4 Atmega103的SPI在FH中的运用 由上述描绘可知,SPI在规划中占有重要的位置,模块内部的首要操控和数据交流都由其完结,下面详细介绍SPI在模块中的规划办法。 4.1 SPI的作业原理 ATmega103和外设之间可经过SPI进行高速同步数据传输。主从CPU的SPI衔接见图2所示。其间,SCK为主机的时钟输出和从机的时钟输入。把数据写入主机SPI数据寄存器的操作将发动SPI时钟发生器,此刻,数据将从主机的MOSI移出,并从从机的MOSI移入,移完一个字节后,SPI时钟中止,并设置发送结束标志。此刻假如SPCR的SPIE(SPI中止使能)置位,则引发中止。挑选某器材为从机时,可将从机挑选输入端SS拉低。主从机的移位寄存器可以看成是一个分布式的16 位循环移位寄存器。当数据从主机移向从机的一起,数据也将从从机移向主机,从而在移位过程中完结主从机的数据交流。 SPI的首要寄存器包含操控寄存器SPCR、状况寄存器SPSR、数据寄存器SPDR。其间SPCR用于设置SPI的中止使能、数据传输次序、主从机挑选、时钟相位和时钟速率等;SPSR为SPI中止标志,用于标志写抵触。SPDR寄存器用于在寄存器文件和SPI移位寄存器之间传递数据。写该寄存器时,将先对数据传送进行初始化,读该寄存器时,读到的将是移位寄存器接纳缓冲区的值。 4.2 SPI的程序规划 在该FH信号处理模块中,单片机经过SPI与FPGA交流数据。FPGA选用Xinlix公司的XCV100。下面详细介绍几个首要的子程序: (1)SPI的初始化 程序在复位时,一般都要对SPI口进行初始化。单片机设置若为主机。SPI的数据次序为LSB低位在前。SCK时钟空闲时为低电平,在SCK的下降沿采样数据;时钟为体系时钟的1/128。那么,详细的初始化程序如下: reset:ldi rx,$0 out spsr,rx ;清SPI中止标志,写抵触标志 ldi rx,$0f7; out spcr, rx ;设置SPI的传输参数 (2) SPI的发送程序

单片机每次需求把10byte的相关码送给FPGA,因而应将SRAM区的$09c2-$09df段设定为SPI的数据缓冲区,然后由SPI从该缓冲区中取数据直到发送结束。SPI的发送函数如下: spi_send:ldi xh,$9 ldi xl,$0c2; sts spififoo,xl ;将SPI缓冲区的输出地址设为$c2 ldi ry, 10 ;将10byte相关码存入$9c2开端的地址 s67_2: ld rx, y+ ;y为相关码寄存的地址 st x+, rx s67_3: dec ry brne s67_2 sts spififoi,xl ;将SPI缓冲区的输入地址存入spififoi ldi rx,$0aa ;将发相关码的标志$aa经过SPI out spdr,rx ;送给FPGA sei ;开中止 ret (3) SPI的中止程序 每次SPI发送完一字节,都要发生一个中止,以使程序跳转到SPI的中止程序。因为SPI主从机的移位寄存器可以看成是一个分布式的16 位循环移位寄存器,并且在当数据从主机移向从机的一起,数据也从从机移向主机,故在中止程序中,应首要判别SPDR中的数据是否是需求接纳的数据(相关值),然后判别SPI缓冲区中的数据(相关码)是否发完,如没有,则持续发送,直到发完停止。详细程序如下: spi_int:push xl ;保存寄存器的值 push xh in xl,sreg push xl lds xl, rcormark ;判别是否为有用数据,“0”为有用 brne spi_2 不等于0,跳 in xl, spdr sts incorbuf, xl ;将相关值存入incorbuf spi_2: lds xl, spififoo ;比较缓冲区的输入,输出指针 lds sprx, spififoi cp xl. sprx ; breq spiend ;持平,则数据发完,跳 ldi xh,$9 ;不等,则取下一个字节送入spdr ld sprx, x+ out spdr, sprx cpi xl, $0e0 ;调整spififoo指针 brlo spi_0 ;未超越缓冲区规模,跳 ldi xl, $0c2 ;超越,将缓冲区开端地 址给spififoo spi_0: sts spififoo,xl; spiend:pop xl out sreg,xl pop xh pop xl reti 5 结束语 本规划计划已经过软硬件调试,结果表明:AT-mega103单片机较89C5X系列单片机在资源和功用上都有很大的进步,不光操控愈加简略、灵敏,并且可以节约不少外围电路,因而具有本钱和体积上的优势,可彻底满意跳频信号处理模块的功用要求。