(原文来历:微计算机信息 李森;张春熹;李保国;林恒 在此特别道谢!)

1 导言

选用光纤陀螺的捷联惯性导航体系是一种极具发展潜力的导航体系,关于其间心部件的光纤陀螺,尤其是中高精度光纤陀螺,环境温度带来的漂移是不容忽视的,因而对体系进行温度操控很有必要。温度操控电路是整个温控体系的硬件根底,其间涉及到温度收集,与微处理器通讯,串口输出,操控数模转化芯片等多个组成部分。本文提出一种高效有用的FPGA接口规划,它能够完结和谐各个组成部分有序作业,精确、快速完结数据传输,严厉操控信号时序等作业。

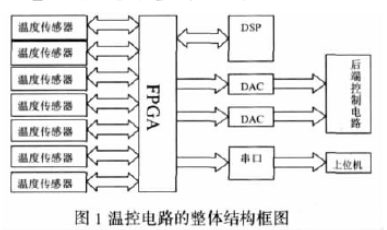

温控电路全体结构

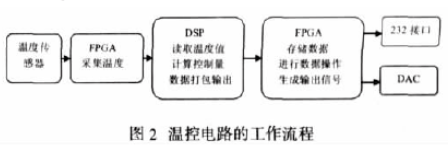

温控电路的全体结构框图如图 1所示。其间包括七路温度传感器,DSP, 232接口芯片,DAC ,后端操控电路,上位机和FPGA等多个组成部分。FPGA接口是整个电路的中心。 其间,温度传感器选用 DALLAS公司的 DS18B20,它选用 1-wire总线协议,仅需 1根数据线进行通讯。DSP选用 TI公司的TMSVC33,它能够完结高速浮点运算。232接口芯片选用MAXIM公司的MAX3232,支撑高达 120kbps的传输速率。DAC选用 TI公司的TLV5620I,它是通过 4条串行信号操控的 8位 4路数模转化芯片。FPGA选用 ALTERA公司的 ACEX系列的EP1K100,它时钟频率高,具有丰厚内部资源,供给很多可编程 IO管脚,装备十分便利。依据 FPGA的温控电路接口在整个电路中具有十分重要的效果。FPGA自身的高速并行结构为整个电路的功用供给了牢靠确保。 温控电路作业流程 温控电路的作业流程如图 2所示。FPGA与七路温度传感器通讯,读取温度值,并存储于内部存储器中,每秒更新一次。FPGA发送中止信号告诉 DSP读取 FPGA中存储的温度值,DSP依据当时温度值和操控算法计算出操控量。然后将温度值和操控量打包成一帧数据发送

给 FPGA。FPGA将DSP发送来的数据存储在内部存储器后,对数据进行操作,生成输出信号。FPGA一方面将数据串行发送给 232接口芯片,然后通过 232串口发送给上位机。上位机可通过监督软件实时观测温度值和操控量的改变状况,便利体系调试与评价;另一方面从数据中提取出操控量,将其串行输出到DAC,数字操控信号通过 DA转化后输出模仿操控电压到后端操控电路,完结对七路温度的闭环操控。

4.FPGA与外围电路之间的通讯接口 FPGA与外围电路之间的通讯接口首要包括与温度传感器,DSP,232接口芯片和 DAC的通讯接口四个部分。

(1) 与温度传感器的通讯接口

本方案的温度传感器选用DS18B20,它通过硬件十分简略的 1-wire总线通讯,因为硬件简略所以通讯协议比较杂乱。要完结与它的通讯接口将占用很多 FPGA片内资源,并且本方案要进行七路温度收集,因而优化程序规划,削减冗余,节约资源显得尤为重要【2】。

(2) 与 DSP的通讯接口

DSP与 FPGA的组合已经成为当今数字电路中十分盛行的方式。FPGA十分合适与 DSP合作。本方案中,DSP与 FPGA的通讯接口首要由数据总线,地址总线和一些操控信号组成。FPGA和 DSP之间由 8位数据总线衔接,数据以字节方式并行传输。DSP通过地址总线对 FPGA的片内资源寻址。操控信号首要包括复位信号,中止信号和读写信号。

(3)与232接口芯片的通讯接口 FPGA与 232接口芯片的通讯是通过收发两条数据线完结的。本方案中,只存在温控体系到上位机的单向数据传输,故仅需一条发送数据线就能够完结与 232接口芯片的通讯。

(4)与 DAC的通讯接口

本方案选用 TI公司的TLV5620I芯片作为 DAC。它是8位4路电压数模转化器。关于它的数字操控依据由 4条信号线组成的串行总线。包括 CLK,DATA,LOAD和LDAC四种信号。 5FPGA的逻辑规划

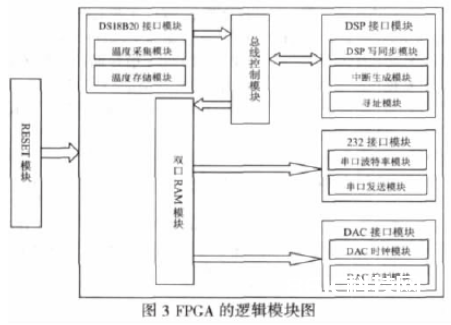

在温控电路的总体方案,硬件结构,作业流程和接口协议都确认后,就能够进行 FPGA的逻辑规划了。FPGA的逻辑规划是整个温控电路接口规划的重中之重。它依据 verilog硬件描绘言语。杰出的 FPGA逻辑规划应该是时序明晰,运转安稳,成果清晰和节约资源的。它能够确保整个体系的牢靠,安稳和高效。FPGA的逻辑模块图如图 3所示。FPGA内部逻辑大致分为 RESET模块,DS18B20接口模块,总线操控模块,DSP接口模块,双口 RAM模块,232接口模块和 DAC接口模块等几部分。

(1)RESET模块 该模块生成大局复位信号。是一切模块中优先级最高的。体系上电后,该模块将复位信号拉低并继续 1秒然后拉高,对 DSP和 FPGA内部其他模块进行复位。

(2)DS18B20接口模块 该模块用于完结与 DS18B20通讯,读取并存储温度值。它包括 2个子模块。

一、温度收集模块

该模块完结与 DS18B20的通讯协议。首要通过一个初始化序列对 DS18B20进行初始化,包括一个由主机宣布的复位脉冲和其后由从机宣布的存在脉冲。探测到存在脉冲之后,代表初始化完结,模块将发送 ROM操作指令。本方案中,履行 SKIP ROM越过 ROM匹配。之后将发送存储器操作指令。温度转化和读取温度就在这部分完结。其间每一次读写操作都需求严厉依照 DS18B20的读写时隙进行。该模块杂乱程度高和占用资源多,是整个 FPGA中的重要模块。本方案一共有七路温度收集模块,它们的并行结构使得体系能够便利地完结对七路温度的实时监控。 二、温度存储模块

该模块的首要构成部分是一个 14*8位存储器,用于存储七路温度数值,每一路数值需求2个8位寄存器寄存。存储结束后,等候DSP读取。

(3)DSP接口模块该模块首要用于与 DSP进行通讯。它包括 3个子模块。 一、DSP写信号同步模块 DSP的数据写入在写信号操控下完结。因为 DSP和 FPGA选用不同的时钟源,所以 DSP发生的写信号无法和 FPGA的主时钟同步。这样就会导致写数据过错。该模块用于将 DSP写信号与 FPGA的主时钟同步。 二、中止生成模块 因为本方案中,温度值每秒更新一次。在温度值更新后,通过中止信号告诉 DSP读取温度值。该模块用于生成周期为 1秒的中止脉冲。

三、寻址模块 该模块对 FPGA片内资源进行编址,由 DSP的地址总线操控寻址。精确读写所需的数据。

(4)总线操控模块 DSP和 FPGA之间的数据总线是双向总线,总线操控模块用于操控总线的数据流向。当DSP从 FPGA中读取温度值时,总线操控模块将温度存储模块和数据总线相连,输出数据。当 DSP向FPGA中写数据时,总线操控模块将数据总线和双口 RAM模块相连,输入数据。

(5)双口 RAM模块 该模块首要完结以下三个功用:当 DSP写数据时,将数据存储于内部存储器中;当数据存储结束后,将其间的操控量发送给 DAC操控模块;与串口发送模块通讯,将一切数据顺次串行输出。

(6) 232接口模块 该模块用于完结串口数据输出,它包括 2个子模块: 一、串口波特率模块 串口通讯协议要求数据收发两边有相同的波特率。该模块用于设定串口通讯波特率。 二、串口发送模块

双口 RAM模块将数据存储结束后,将给串口发送模块一个标志信号。串口发送模块接到此信号后,顺次将双口 RAM模块中存储的数据串行输出。

(7)DAC接口模块 该模块包括 2个子模块: 一、DAC时钟模块 DAC需求特定频率规模的时钟来驱动。该模块用于生成驱动 DAC的时钟信号。 二、DAC操控模块

该模块用于生成DAC操控信号。它的基本原理是将双口 RAM模块输出的 7路操控量存储在内部存储器,然后依据 DAC的接口协议生成 CLK,DATA,LOAD和 LDAC等操控信号,这些信号将驱动 DAC的作业,将数字操控量转化成模仿电压值。

结束语

FPGA接口规划需求归纳考虑硬件衔接,作业流程,接口协议和逻辑模块等多方面要素,是一项体系工程。本文分别从以上几方面介绍了依据 FPGA的光纤陀螺惯导体系温控电路接口规划,该规划现在已使用于实践体系中。通过验证,接口满意体系要求,作业状况杰出。本文所述的 FPGA接口规划方案是牢靠,安稳和高效的。可为其他相关使用供给有利的学习。本文作者立异点:七路并行温度收集结构;多功用温控电路接口结构;温度值和操控量打包解包数据传输协议;高效安稳的多接口 FPGA逻辑规划;

责任编辑:gt