在操控范畴中,PID操控足最早开展起来的操控战略之一,因为其算法简略、鲁棒性好和牢靠性高,被广泛运用于工业进程操控。此外,跟着操控理论的开展,专家体系、含糊逻辑、神经网络、灰色体系理论和传统的PID操控战略相结合又派生出各种新式的PID类操控器,构成巨大的PID宗族,许多算法大大改进了传统P1D操控器的功用。但是,这些算法在工业中的实践运用规模却远远落后于传统PID算法,其间一个原因就足传统的单片机加分立元件构成的工业操控体系在施行更新更杂乱的算法时,算法的杂乱性或使得体系硬件规划调试愈加杂乱,或使得单片机内软件代码行增多,延时加大,开发周期变长。稳定性和牢靠性在新体系设计时成为不能忽视的一个问题。

而近年来,微电子技能的迅速开展,使得集成电路规划和工艺水平有了很大的进步,跟着超深亚微米技能的开展,使得原先由许多IC组成的电子体系集成在一个单片硅片上成为或许,构成所谓的片上体系(System 0n Chip,SOC),一起也促进了相应EDA东西的蓬勃开展。

操控算法的极大丰富和微电子范畴工艺技能及EDA东西的飞速开展,使得咱们能够将两个范畴的运用优势调集在一起,在EDA东西的协助下快捷快速地在FPGA上牢靠地完结各种新式算法,完结整个操控体系从行为算法级(体系级)到物理结构级的悉数规划,然后到达将各种新式PID算法广泛运用于实践工业操控体系的方针。

2、离散PID操控算法

2.1 PID算法

份额、积分、微分(PID)操控是操控体系中技能最老练,运用最广泛的一种操控办法。其根本原理是依据反应操控体系的差错值按份额、积分、微分函数联系进行运算,所得成果输出给履行机构,履行机构依据差错值的运算成果来操控被控目标。在接连时刻域中,PID操控器算法的表达式为:

![]()

其间:e(t)为操控器的输入即操控体系的给定量与输出量的差错;u(t)为操控器的输出;Kp为份额系数;Tl为积分时刻常数;TD为微分时刻常数。

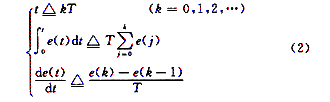

2.2 PID算法的离散化

因为核算机操控只能依据采样时刻的差错值核算操控量,因而需对上式进行离散化处理。按模仿PID操控算法度(1),以一系列的采样时刻点kT代表接连时刻t,以矩形法数值积分(和式)近似替代积分,以一阶向后差分(增量)近似替代微分,即:

可得离散PID表达式:

![]()

式中,积分系数K1=KP/Tl,微分系数KD=KPTD,T为采样周期,k为采样序号,k=1,2,…,e(k一1)和e(k)分别为第(k一1)和第k时刻所得的差错信号。

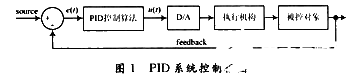

2.3 PID操控体系框图

一般操控体系的PID体系操控框图如图1所示。其间,source为体系设定值,feedback为体系反应值,e(t)为反应差错,u(t)为PID操控器输出值。图中“PID操控算法”框图子体系即需求咱们在算法级用DSP Builder进行自顶向下的规划仿真。

3、依据DSP Builder的PID操控体系FPGA规划过程与开发

3.1 Simulink东西箱的A1tera DSP Builder 组件

在运用FPGA进行体系的开发运用上,已有了全新的规划东西和规划流程。DSP Builder。便是Altera公司推出的一个面向DSP之类的芯片级开发的体系级东西。他是作为Matlab的一个Simulink东西箱(Tool Box)呈现的,他使得用FPGA规划专用芯片体系彻底能够经过Simulink的图形化界面进行,只需简略地对DSP Builder东西箱中的模块进行调用即可。值得注意的是,DSP Builder中的根本模块是以算法级的描绘呈现的,易于用户从体系或许算法级进行了解,乃至不需求非常了解FPGA自身和硬件描绘言语。这为传统操控体系范畴的工程师开发依据FPGA/ASIC的牢靠操控体系芯片自顶向下的算法级规划供给了便当的条件。

3.2 在Matlab顶用DSP Builder完结顶层算法规划

规划办法能够从与硬件彻底无关的体系级开端,首要运用Matlab强壮的体系规划、剖析才能和DSP Builder供给的模块(或IP核)完结顶层体系规划及体系仿真测验。

依据图1的原理,在Matlab中进行规划仿真,Simulink顶层规划模型如图2所示。

在顶层规划模型中,除“PID操控子体系”外,其他部分均选用一般Simulink组件规划。为了在验证仿真时更靠近实践体系,给被控目标加上可调延时深度的延时即节。信号发生器给出体系设定值,对一般实践运用的操控体系而言,能够运用典型的矩形波,这儿用数个矩形波与正弦波的叠加来仿真体系设定值的给出。

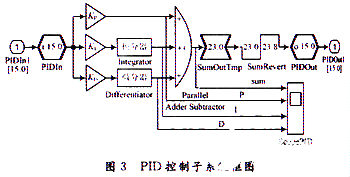

模型中的“PID操控子体系”完结PID算法部分。该子体系经仿真规划后,将经过DSP Builder中的SignalCompiler转化为FPGA的HDL 言语规划,所以这部分除了仿真调查所需的示波器等外需悉数选用DSP Builder组件来规划,不然Signal Compiler编译时不能辨认。

为了简略地阐明如何用DSP Builder自顶向下的规划依据FPGA的操控体系,这儿用一般的方位式PID算法进行举例。方位式PID算法的PID操控子体系规划框图如图3所示。

在图3中,输入差错信号选用了16位精度。而为了完结份额、积分、微分系数的准确可调,在这儿PID系数选用了8位精度,使系数至少能够准确到百分位。一起,在体系规划进程中为了尽量防止浮点数的运算,这儿将PID系数取成整型,先放大数据值到24位,而在并行加法器运算单元后用IO&Bus中的总线转化器单元对累加后的数据进行位数转化,完结FPGA中的浮点数运算。

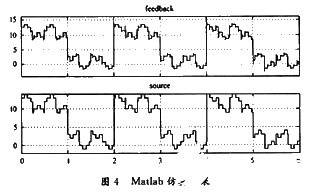

Matlab仿真成果如图4所示。其间,source为体系设定值,feedback为体系反应值。

波形仿真成功后,需求将Matlab中图形化的顶层规划模型转化成能够被FPGA开发软件辨认的HDL言语描绘文件。在图2中,翻开Signal Compiler模块,装备相关参数,能够将DSP Builder 规划的“PID操控子体系”编译成VHDL及Veirlog言语的RTL表述和东西指令言语Tcl脚本。依据编译信息前面的规划模型,直到编译陈述中Convert Mdl to VHDL,Synthesis,Quartus II Fitter三项状况均为PASSED,即可取得ModelSim所需的tb_SystemName.tcl功用仿真文件脚本和Quartus所需的SystemName.qpf 项目文件和SystemName.vec 仿真波形文件。

3.3在ModelSim中完结HDL代码功用仿真

在ModelSim菜单中履行Tools一》Execute Macro,翻开前述Signal Compiler编译生成文件tb_System-Name.tcl(VHBL)或tb_vo_SystemName.tcl(Verilog),调试成功后,仿真得到图5成果。功用仿真成果与Matlab中根本共同,证明顶层规划根本成功。

3.4 在Quartus中完结FPGA开发

在Quartus中翻开前述Signal Compiler编译生成文件SystemName.qpf。设定相应器材Device,在Tcl Scripts中运转SystemName_quartus.tcl装备此工程项目变量,然后编译。调试成功后,载入SystemName.vec波形仿真文件运转时序仿真东西,得到图6成果,与图5根本相符,证明规划成功。

4、结 语

这儿给出了一个开端用于FPGA的体系级规划东西DSP Builder在自动操控范畴的运用,现在在已出书的国内期刊及论文库中好像还没有相关文献谈到这个穿插范畴的运用。

在操控范畴里,当各种杂乱的新式PID算法运用于实践操控体系中时,因为传统单片机与分立元件电路体系的局限性,硬件目标和软件杂乱度都使得新的运用及研制规划发展缓慢;一般FPGA/CPLD没计又存在着没计周期长、可重复运用性差等缺陷。咱们将日益完善的SoC规划东西运用于自动操控范畴,不仅在算法规划上有了新的方便快捷的规划东西,一起籍由FPGA硬件自身的长处也能够处理单片机及分立元件存在的电磁搅扰、体系杂乱度高级各类问题,然后大大进步将各种新式PID算法广泛运用于实践工业操控体系的可行性。

在体系规划中进一步的讨论:因为规划是从与硬件彻底无关的Matlab体系级仿真开端,因而便于传统操控范畴工程师们能够迅速地将算法级的构思运用于操控体系规划中,然后能够将有限的精力专心于体系级算法的规划,而防止堕入重复繁琐的电路规划中去,缩短从人脑构思到实践体系完结的时刻周期。其间单个规划MDL文件乃至能够考虑封装成“算法包”的方式进行资源重复运用,以完结功用单元的快捷增减和缩短产品开发时刻。这儿或许存在着操控范畴里可重用算法及相应“包”的接口规范。这种状况或许和SOC范畴IP核的现象有部分相似,本文就不再多述。

责任编辑:gt