1、ADC10065的首要特点

ADC10065是美国国家半导体公司推出的一款低功耗、单电源供电的CMOS 模数转化器。该芯片在3V单电源供电时,能以65MSPS的采样速率将模仿信号转为准确的10 位数字信号,而功耗仅为68.4mW,其备用形式时的功耗仅为14.1mW。ADC10065片内选用具有数据纠错功用的差分总线结构。因而可在最小的功耗条件下供给极优异的动态功用。该器材可广泛运用于超声波和图画收集、蜂窝基站/通讯接收机、声纳/雷达、xDSL、无线局域网、数据收集体系以及DSP 前端。

ADC10065的首要特性如下:

●3V单电源供电;

●满标度输入摆幅可在2.0 Vp-p,1.5 Vp-p,0或 1.0 Vp-p四种输入信号中挑选;

●具有400MHz-3dB的输入频宽;

●具有静态作业形式;

●带有片内基准源和采样坚持扩大电路;

●具有二进制补码数据格局输出;

●可调整的输出驱动合适2.5V和3.3V系列的逻辑器材接口。

下面是ADC10065的首要参数:

●分辨率:10Bits;

●转化速率:65MSPS;

●FPBW(全功率带宽):400MHz?

●DNL(差分非线性):±0.3 LSB;

●SNR(信噪比fIN=32MHz) :59.3dB ;

●SFDR(无差错动态规模fIN=32MHz时):-80dB;

●数据推迟:6个时钟周期;

●参阅电压:+3.0V;

●65MHz时的功耗为:68.4mW。

2、引脚功用

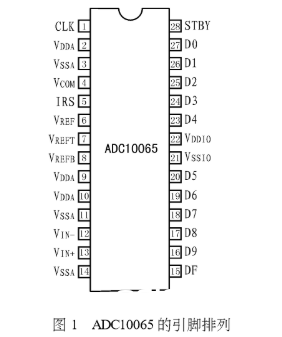

图1为ADC10065的引脚摆放,该器材选用28脚TSSOP封装,各引脚的基本功用如下(括号中为引脚号):

VIN-,VIN+(12,13):模仿信号输入端。在1.2V参阅电压下,满标度输入摆幅为1.0Vp-p。单端操作时,VIN+可与VCOM衔接。

VREF(6):参阅电压(1.5V)引脚,运用时应经过一个1μF的旁路电容衔接到VSSA。

VREFT,VCOM,VREFB(7,4,8):VREFT和VREFB仅为高阻抗参阅旁路管脚,而VCOM则可用作设置输入共用电压VCM,这三个引脚都应当衔接0.1μF的旁路电容。

CLK(1):数字时钟输入端。输入频率规模为10MHz~65MHz,输入在时钟的上升沿有用。

DF(15):该引脚为高电平时,输出为二进制补码,该脚低电平时,输出为偏移二进制码。

STBY(28):静态备用形式管脚。高电平时,该器材转到备用形式。

IRS(5):输入规模挑选管脚。该脚接VDDA时, 满标度输入摆幅为2VP-P,接VSSA时为1.5VP-P,悬空时为1VP-P。

D0~D9(16~20,23~27):数据输出端。D0是二进制输出数据的最低有用位,D9是最高有用位。

VDDA(2,9,10):模仿电源正极。需与一个3V的直流电源相连并衔接一0.1μF的旁路电容到模仿地。电容应紧靠这些引脚,间隔不超越1cm处。一起还应并联一4.7μF的电容到模仿地。

VSSA(3,11,14):模仿地。

VDDIO(22):数字电源正端。该脚也运用一个0.1μF的电容旁路到数字地一起用一个4.7μF的电容并联到数字地。该管脚上的电压不能超越VDDA电压300mV以上。

VSSIO(21):数字地。运用时应与数字地相连并远离模仿地。

3、作业原理

图2为ADC10065的内部结构框图。

该器材由采样坚持、九级差分电路、时钟操控、数字纠错、带隙精细电源、输出缓冲和管状数据线等七部分组成。依据IRS的状况不同,差分输入端可挑选峰峰值为1V、1.5V或2V的模仿信号,其中心值在VCM/2,相位差为180°,可是,差分输入方法可使体系取得较好的功用。芯片内部仅有的一个采样坚持级可供给400MHz的全功耗带宽,数字纠错的多级差分电路则可确保在供给优异动态功用的一起具有较低的功耗。ADC10065内部的+1.2V精细基准电源可用来设置该芯片的输入信号峰值规模。在精度要求较高时,也能够运用外部参阅电源。其10位数字输出格局即能够是偏移二进制码,也能够是二进制补码。

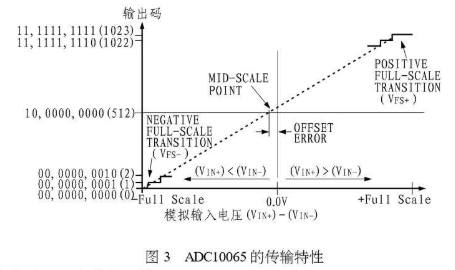

图3给出了ADC10065的传输特性。

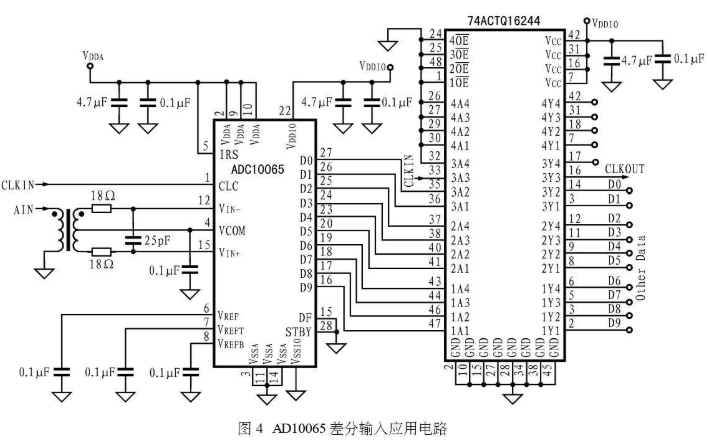

4、运用电路

图4所示是ADC10065的典型差分输入运用电路。图中,ADC10065的两个模仿信号输入端VIN+,VIN-构成差分输入对,共用形式脚VCOM用来设置共用输入电压VCM。ADC10065的作业参阅电压为1.2V,但在0.8~2.0V时仍有优异功用,较低的电压能够下降信噪比,三个旁路引脚VREF、VREFT、VREFB上的0.1μF电容首要用来下降噪声电流。因为模仿输入端内部的开关动作会耗费必定的能量,一起会附加必定的噪声信号,因而,应在每一输入端串接一18Ω电阻,一起跨接一25pF电容,这些元件应尽量放置在接近芯片的方位,输入端是体系最灵敏的部位,一起也是滤波的最终时机。

因为CLK信号用于操控采样进程,因而,该信号应安稳、低颤动,规模应在10MHz~65MHz、上升/下降时间应小于2ns,其引线应尽或许短,不能跨过任何引线,特别不能有90°跨过。CLK信号有时也驱动片内状况机,假如它中止或频率太低,芯片内电容的电荷将放电然后或许引起输出数据精度的下降。CLK的占空比对A/D转化器功用影响也很大,一般要求40%~60%,最好为50%。

ADC010065有10位与TTL/CMOS兼容的输出端,捕捉一位有用数据的简略方法就是在时钟的上升沿锁存数据。当驱动高电容总线时,要特别当心,因为电容的充电效应,驱动的电容越大,瞬间经过VDDIO、VSSIO的电流越大,这个充电尖峰脉冲可引起片内噪声,并或许耦合到模仿电路,以至于下降芯片的动态功用。别的,总线电容也可引起输出推迟时间的添加,然后使得输出数据的锁存变的困难。为了减小噪声,有必要最小化数据输出端的负载电流。为此,可在ADC输出和外接的其它电路之间加一级数据缓冲器。

责任编辑:gt