当今的模数转化器 (ADC) 选用了最新的技能,以高精度及快速的采样频率对模仿信号进行收集。数据转化器的复杂性跟着采样频率及精度的进步而添加。高功用数据转化器规范的设定有必要遵从严厉的输入条件,以完成器材预期功用的最大化。一个颇具应战性的输入条件是:对ADC输入模仿信号进行丈量、驱动和接口衔接。本文将讨论一些关于高速 ADC进行有用接口衔接的技能,然后使ADC完成功用最佳化。

就有用输入驱动以保护信号完整性而言,现已有许多好的运用注释以及文章宣布。本文将讨论有关输入驱动的新发展。

ADC 输入架构与驱动器的挑选

ADC的模仿输入装备跟着采样精度和最大采样频率的改动而有所不同。在输入阶段,影响输入驱动器挑选的特征有:

1. 单端与差分

2. 高阻抗与低阻抗 (100W) (或是有缓冲与无缓冲)

单端与差分

大部分推进采样精度和采样频率抵达极限的ADC选用的是差分输入办法。差分输入的优势在于下降偶次谐波和 EMI。一些差分输入ADC具有IRS(输入规模挑选) 寄存器,其答应运用者经过将未运用的输入衔接到共模 (CM)A/D转化参照的办法,以单端输入来运用器材。

有缓冲与无缓冲

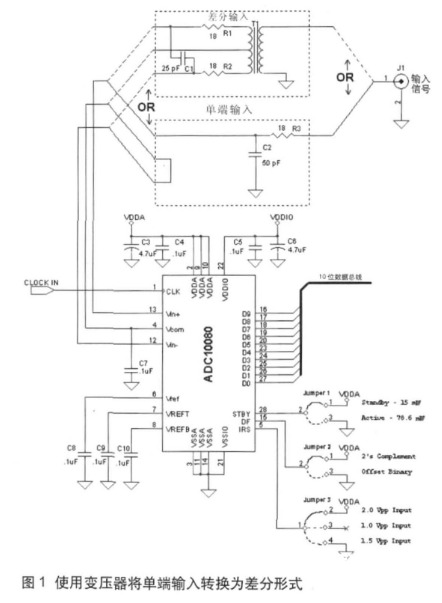

高采样频率ADC (》500 MSPS) 常常要处理高频模仿输入信号。假定运用规范的 PCB板标准和轨道长度,假如这个高频模仿信号没有正常完毕,又用处理射频信号和电路板的办法加以处理,模仿信号就会阑珊。这样的高频运用得益于低阻抗 (50W单端或 100W差分) 模仿输入,因而,大部分 UHF 和 VHF 电路为 50W体系。为了取得较高的失真功用,一般运用差分输入。由于严厉的规范约束,以及受高频的影响,高采样率ADC一般不供给答应运用单端输入的IRS 选项。原因是:选用 IRS 的ADC需求额定的电路才干转化到满量程(FSR),而这关于在高频/高采样率下的运用却并不可行。因而,这个等级的ADC需求高频、低电阻 (100W差分)的输入驱动。运用低电阻输入 ADC,模仿输入在被运用到用于转化的采样/坚持 (S/H) 电路之前就已缓冲。所以,并不需求选用在非缓冲 ADC中运用的规范去耦电路 (串联电阻R,并联电容C)。在图1的图解中运用了一个非缓冲输入的 ADC (ADC10080),这些去耦元件在图中标识为 R1、R2(18W) 及 C1 (25W)。

从单端到差分的转化

中点接线变压器

(Ruthroff 变压器)

如前所述,驱动差分 ADC 的输入有必要为差分方法。将单端输入转化为ADC 可用的差分信号需求运用一个中点接线变压器,如图1所示(在“差分输入”虚线下可看出变压器怎么接到 ADC 输入)。

差分输入的共模电压(CM)应遵从 VCOM 电压(在 ADC 上的输出引脚),以便使 ADC 内部的采样坚持电路正常作业。图1中的电路答应经过将变压器的中点接线衔接到ADC的 VCOM 输出来对输入 CM 加以设定。

变压器的较低截止频率不答应低频内容被耦合进来。因而,这种方法的耦合只可运用于不需求 DC 以及低频内容的体系。除此之外,这个电路也承受了高频变压器的走漏效应,约束了它的上限作业频率。典型的变压器有上限及下限作业频率。较低频率约束由初级电感决议。关于这个与 8 位转化器一同运用的变压器而言,假如不选用其它的增益校准或调整办法,其作业的频带十分窄,受限在 1 MHz ~100MHz,其间,刺进损耗改动小于 0.034dB (1 LSB)。

关于最大回波损耗(最小反射),许多较高速度的运用要求对图1中 J1 (输入衔接器)处的输入阻抗进行操控,而且要与衔接到衔接器的电缆特征阻抗相匹配。当电缆的长度超越所遇最短波长的 1/20时,这种要求尤为重要。只需变压器回波损耗在频率极值时功用没有阑珊,就有或许经过设置一个经过输入的终端电阻 RT 来到达此方针。这样,输入阻抗就会挨近RT,原因在于变压器回波损耗已增大,足以具有最小负载效应。在较高的频率下,由于变压器回波损耗的削减,运用这种类型的变压器装备会使操控输入端愈加困难。而这正是不平衡变压器的优势地点。

不平衡变压器

(Guanella变压器)

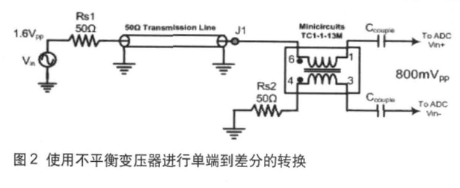

另一个进行单端到差分转化的办法是运用不平衡变压器,如图2所示。

与图1比较,这种办法具有下述长处及缺陷:

长处:

1. 较高的作业频率

2. 关于宽带运用而言,有较高的回波损耗

3. 较佳的增益与相位平衡

缺陷:

1. 无法设定共模电压

2. 无法供给电压增益

与图1的中点接线变压器或 Ruthroff 变压器比较,不平衡装备有着更高的作业频率。但是,选用不平衡装备后,由于无法设定共模电压水平,ADC 输入有必要为 AC 耦合电压。以ADC08D1500为例,它是一个 8 位、1500MSPS 的转化器,假如在 AC耦合的方式下作业,就会经过内部电阻主动将其输入端偏置到恰当的共模电压值。假如ADC的 VCMO 输出接地,就会以 AC 耦合方式运转。

如图2所示,运用 AC 耦合电容 (4.7nF),输入耦合电路的-3dB频率大约为 677 KHz (=1/(2pReqCeq),其间,Req=100W,Ceq=4.7nF/2=2.35nF)。这个 100W的等效电阻是耦合电容器 (RT2与 ADC 的 100W输入并联,一共 50W) 右边的差分负载与介于不平衡变压器引脚1 和引脚3(50W)间差分阻抗的串联组合。

选用图2的电路,J1终止于 50W 左右,而且假定所驱动的ADC具有100W的差分输入终端(如 ADC08D1500)。与 100W ADC输入阻抗并联的 RT2为 50W,这是从 J1 到接地的输入阻抗。此输入阻抗一向坚持必定的频率,然后使不平衡变压器发挥变压器的效果。超越这个依据特别不平衡变压器及其间心特征、线圈间电容,以及其它因数的频率规模,输入阻抗就会违背这个值,而且输入反射会导致回波损耗削减。大部分不平衡变压器的产品手册都列出了几个频点的回波损耗与上限和下限作业频率。

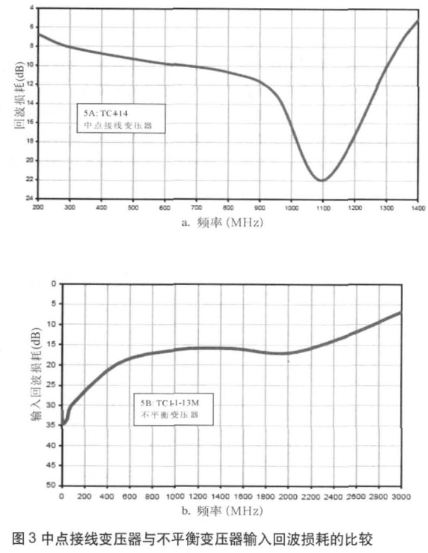

图3显现了一个中点接线变压器 (TC4-14) 以及一个不平衡变压器 (TC1-1-13M) 的输入回波损耗,并进行了简略的比较。

由图3中能够看出,中点接线变压器的回波损耗在 700MHz 以下与 1.3GHz 以上时,下降得十分敏捷,而不平衡变压器则具有必定的高出数 MHz 的回波损耗 (》 10dB),而且在频率抵达约 2.6GHz 左右时才开端下降。这是不平衡变压器相关于中点接线变压器的长处。在较高频率削减的回波损耗会构成一种不匹配的状况,而且发生较高的反射能量,这会在收集信号中构成不想要的谐波,而且下降体系的 ENOB 功用。

回波损耗 (RL)与 二端口输入阻抗相关,如式1如示:

RL= 20 Log | (Zin+50)/ (Zin-50)| (1)

举例来说,10dB 的 RL 与96W 或 26W的输入阻抗相符合 (依据式1中商的符号而定)。阻抗不接连时的反射波(图2中的 J1)在源端出来另一个反射之后将会抵达 Rs1 (假定来历与传输线并没有完美匹配)。往复时刻为 l/n,其间,l为电缆长度,n为经过传输线介质的波速。构成输入信号的不同频率元件,在遇到此往复推迟而且加上本来的入射波之后会回到中止处,然后构成终究的信号。关于往复推迟 (2l/n),l为一个重要的谐波(大约是周期 T 的 1/10),其终究的波形将会失真。从数学上讲,这儿的T满意了 T ≤ (20 l/n) 的谐波要求。原因是,关于较短周期的谐波,入射以及反射波会组成(在时刻上)交迭方法,这会构成波形的改动。这正是在 ENOB 上下降的原因,由于这个改动的波形将会添加总谐波失真 (THD) 的失真项,然后发生较低的 ENOB。

为了平衡非平衡功用,变压器的初级与次级总会坚持1:1 的份额,因而,此装备不能供给任何电压增益。

有源单端到差分的转化

如前所述,变压器能够被用作转化器,但是它们在宽带的运用上有很大的缺陷,而且在这些运用中,它们不会在其操作频率区域中包含 DC 和低频。依据这个原因,半导体制作商现已导入了有源器材来履行这项功用,以补偿变压器耦合结构的缺陷。

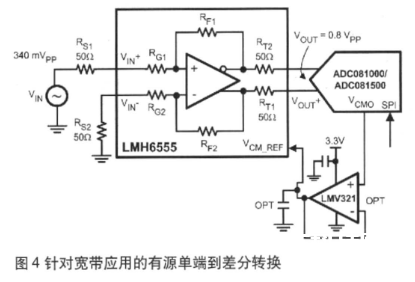

LMH6555 是专门规划用来驱动如图4显现为 0.8Vpp的ADC的 100W差分输入,而且供给一个到终端电缆的固定 50W的输入阻抗(未显现于图4中),以抵达最高的回波损耗。单端到差分转化器会将频率规模从DC一向扩展到1.2GHz(此为 LMH6555 的 -3dB 频宽约束)。经过将ADC的 VCMO衔接到 LMH6555 的 VCM_REF 输入,能够坚持准确的输出共模电压操控。使用这样的结构,能够取得全信号频谱,而共模操控则能够由 LMH6555 主动完成。图4中所示的缓冲器 (LMV321) 用来进步ADC的 VCMO 引脚所流出的电流,以使得关于 VCM_REF输入而言有恰当的驱动才能。是否需求缓冲器取决于ADC的电流输出才能。

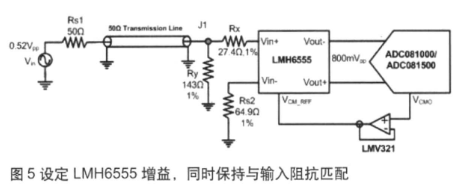

LMH6555 的增益(在Vin+下的差分输出到单端或取决于所驱动输入的Vin+)确认在 4.8V/V,其装备如图4所示,其间,Rs1=Rs2=50W。关于输入信号在振幅上较大的景象,LMH6555 刺进增益能够经过添加 Rs2和 Rs1的值来下降。这两个电阻应该总是持平,以坚持关于低输出偏移的输入平衡。图5所示比如中,坐落 50W电缆接纳端的 LMH6555 的增益经过 Rx 和 Ry下降。经过挑选组件值,LMH6555 电路(J1)的输入阻抗被坚持在50W,以使阻抗匹配。两个 LMH6555具有 100W的到地等效阻抗,各个组成值都被显现,以用来坚持低输出偏移电压。LMH6555的输入/输出摆幅联系如式2所示:

Vout (Vpp) = Vin (Vpp) * [ RF/ (2Rs+Rin_diff)] (2)

其间,RF= 430W,Rin_diff=78W,都是LMH6555 特定的值。

图5 设定LMH6555增益,一起坚持与输入阻抗匹配

Rs是等效电阻,使 LMH6555 的输入接地(假定它们持平)。添加 Rs会下降增益。重新整理式2,答应运用者决议 Rs的值,能够确认关于一个给定 Vin (Vpp) 的全ADC的输入摆幅,如式3所示:

Rs=Vin (Vpp) * 268.8 – 39 (3)

在图5中,LMH6555的等效输入电阻经过 Rs被添加到100W(由式3核算得出),因而,0.52Vpp输入会导致ADC输入刚好为 0.8Vpp,而J1的等效输入则坚持在 50W。

LMH6555将坚持低噪声 (参照19nV/RtHz输出的平带),并与它输入的Rs无关。这是由于 LMH6555 的输入架构由等效输入噪声电压决议,而且独立于源电阻。

ADC要求差分输入的共模电压(在 +/-50mV内)十分挨近它所发生的 VCMO 参阅输出。这是选用1.9V供电电压的一个成果,由于丢失的供电电压下降了ADC内部的电压余量。假如未能坚持此共模操作,ADC的全失真功用将会敏捷恶化。

除了这种共模现象外,ADC两个输入端的任何增益和相位不平衡都会导致获取过错信号。举例来说,一个 100MHz的方波将会在它的尖峰值有 1.5% 的过错。8 位数据收集具有全标准 0.39% 的 LSB,而且不平衡变压器等效于3.8LSB。所以,将增益和相位不平衡最小化是十分必要的。

结语

作为高速ADC接口信号的单端到差分转化,关于重要的数据收集使命,本文剖析了输入信号接口的应战,并讨论了不同的技能需求。

责任编辑:gt