接纳端RX电接口测验

接纳端一致性测验:

(摘自USB3.0 Electrical Compliance Methodology White paper Rev0.5)

测验原理:在履行一致性测验的时分,测验DUT会被设置成环回形式(loopback),码型发生器会宣布带有颤动的一致性测验码型,经过参阅通道,参阅线缆送入接纳端。DUT会将码型发生器送入的波形从头环回输出,假如码型输出与输入有差异,会回来过错计数。

假如DUT支撑内部BERT,经过内部BERT能够直接计算过错,然后将其输出,假如DUT不支撑内部BERT,就需求供给外部协议分析仪器进行误码勘探,然后解码得出计数成果。两种办法各有好坏:内部BERT性价比高,测验较为便利,局限性在与只能支撑CP0码型;外部BERT需求别的装备协议分析仪,但测验码型能够别的支撑CJPAT,PRBS等其他码型。

DUT在环回形式下处理BERT的指令:BRST(测验复位),BDAT(开端测验数据),BERC(误码查询),其间BRST,BDAT在该形式下环回输出,BERC并没有相同环回输出,而是被BCNT(误码计数)替代输出,BCNT中包括有过错信息。

运用AWG恣意波形发生器进行误帧测验的初始化进程是这样的:首要宣布PING.LFPS(此为低频周期性码型用以链路练习,能够运用恣意波形发生器如AWG7000B或许函数发生器AFG3000宣布该波形来切换DUT测验码型:CP0->CP1->CP2->….CP8->CP0以进行不同项目的测验); 接着宣布TSEQ,用于接纳端均衡器练习,CDR 确定,练习链路极性回转;宣布TS1序列将链路装备为回环和加扰形式;宣布BRST测验复位指令,BDAT开端测验数据;接下来就能够发送加扰的带有Rj 和Dj 的D0.0 码型了,在Dj 中包括了USB3.0标准要求的参阅通道的ISI 和Sj;终究宣布BERC误码查询指令进行误码计数查询。

支撑内部BERT的DUT测验办法:

假如DUT支撑内部BERT,测验能够经过AWG7000B系列恣意波形发生器从RX端输入带颤动的受损波形,经过内部BERT,DUT能够记载过错个数,将其从TX端的输出BCNT,能够运用带有PTD(协议触发解码)软件的DSA70000B系列的示波器直接解码BCNT,计算过错计数。该办法运用DUT内部BERT,能够进行外部误码勘探,因此不需求运用误码分析仪,操作相对简略。性价比较高。

运用软件通道仿真的支撑内部BERT的接纳端测验衔接图

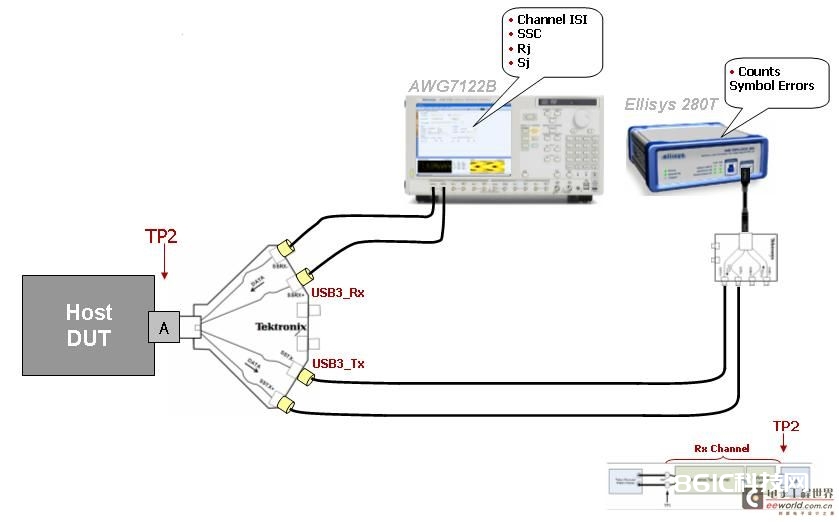

外部BERT的DUT接纳端测验办法:

假如DUT不支撑内部BERT环回,能够运用协议分析仪进行过错检测,上图显现运用Ellisys 公司供给的280T协议分析仪捕获TX的环回码型,进行协议解码,终究得到过错计数。运用协议分析仪能够满意USB3.0的TX和RX端别离选用异步的参阅时钟的要求,能够动态的刺进或许删去码流中的SKP码型,来补偿时钟的相差。

进行接纳端颤动容限测验

当进行颤动容限测验的时分,除了发送端和接纳端的参阅时钟有必要参加SSC以外,预加剧电平设置为-3dB,电压设为0.75V,DUT设置为环回形式,测验需求注入确定性颤动Dj(确定性颤动的改动是经过改动每次注入Sj完成)和随机颤动(Rj不变)。测验点在TP1注入颤动的要求如下:

| Frequency | SJ | RJ |

| 500kHz | 400ps | 2.42ps |

| 1MHz | 200ps | 2.42ps |

| 2MHz | 100ps | 2.42ps |

| 4.9MHz | 40ps | 2.42ps |

| 50MHz | 40ps | 2.42ps |

关于进行USB3.0 的开发用户,公司现在现已供给了用于前期商场开发的根据EXCEL表的USB3.0 RX颤动容限测验主动履行软件ATE(Automated Test for Excel),以满意用户进行比如Receiver jitter tolerance test 以及更高要求的Receiver Margin test等方面的测验要求(其测验颤动频率能够到100MHz,488MHz,860MHz乃至更高)。