一、串行数据体系的根本知识

跟着串行数据速率的不断提高,串行数据体系的传输结构也不断的产生着改动以习惯高速传输的要求:

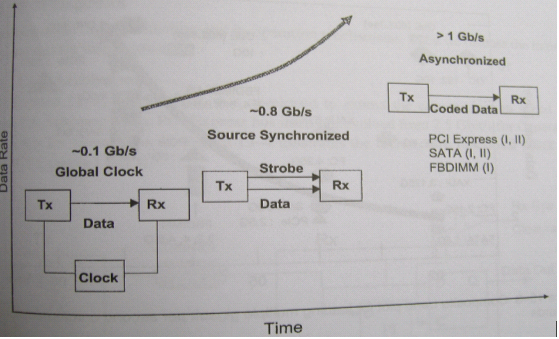

下图1所示为不同的数据速率所对应的体系传输结构:

图1不同数据速率下对应的体系传输结构

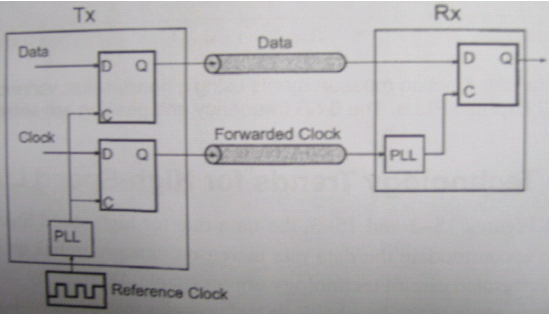

从左到右依次为大局时钟体系结构、源同步时钟体系结构、嵌入式时钟体系结构,跟着数据速率的进一步提高,还有或许呈现其它多种结构,如下图2的前向时钟体系结构,在10Gbps以上的串行数据传输体系中很或许会运用这种传输结构

图2前向时钟体系结构(Forwarded Clock System)

从上图1中能够看出:

1、典型串行数据传输体系首要构成要素包含:发送端TX,接纳端RX,时钟信号及其传输通道,数据信号及其传输通道

2、跟着数据速率的提高,串行数据体系传输结构产生的改动首要会集在时钟信号及其传输通道的改动,在当时新一代的串行数据体系中,如PCI Express(I,II),SATA(I,II)等,现已没有了专门的时钟信号传输通道,而是将时钟信号嵌入到了数据中进行传输,因而需求在接纳端能有用的将时钟康复出来

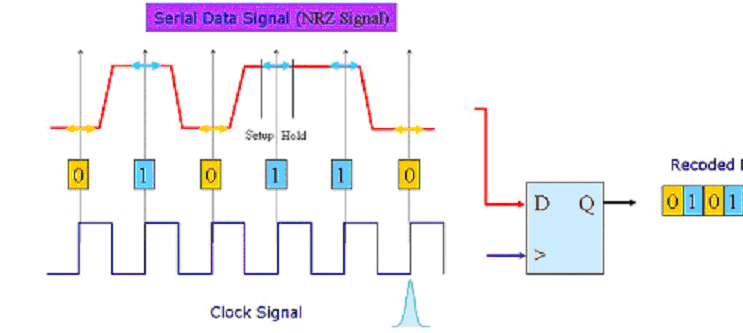

那么为何数据速率的提高需求改动时钟信号及其传输结构呢?了解下接纳端芯片的根本作业原理会有助于咱们了解这些改动。 通讯体系的本质是通过一段介质发送或许接纳数据。发送端TX宣布不同编码方式的高速串行数据,通过一段链路传输后抵达接纳端RX,串行数据在传输进程中会遭到各式各样的搅扰,引起数据的颤动,串行数据体系作业的意图便是要尽或许的削减这些搅扰的影响使得接纳端能准确无误的康复出发送端发送过来的数据。如下图3所示,

图3串行数据体系中接纳端接纳数据的图示

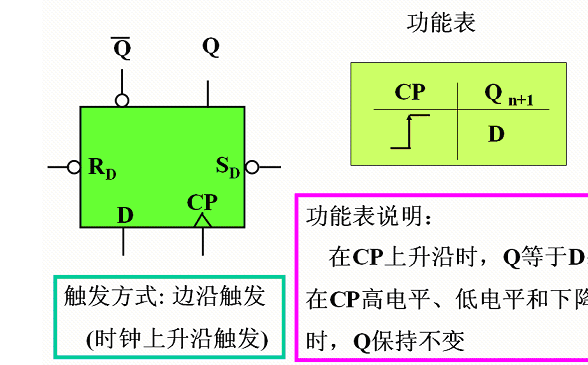

因为接纳端(一般是由D触发器构成)需求运用时钟采样来完结同步接纳数据,因而时钟信号和数据信号之间的同步联系是非常重要的,即必需要满意必定的树立时刻和坚持时刻。因而串行数据时钟体系结构的改动最根本上是为了满意时钟与数据之间的时序联系,以便接纳端能正确的接纳到信号。接纳端D触发器的作业原理

图4 D触发器的根本功能