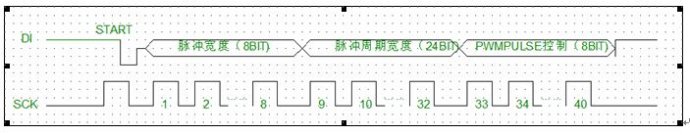

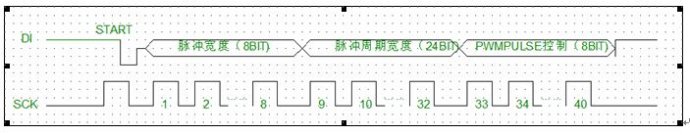

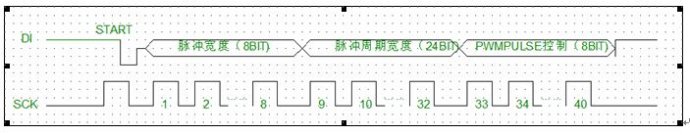

1.线路状况:在平常不发送数据的时分,DI 为高电平。SCK为低电平。

2.开端位:SCK 为高的时分,DI 的下降沿决议了一次数据传送的开端。也就是说,在发送数据的时分,SCK为高电平的期间,DI 不允许改变。

3.开端位有用后,SCK的上升沿输出数据。

4.时序图

5.一切数据低位在前

数据为单向发送,意图是发生宽度可频率能够调理的信号。一起发生一路Pwm信号,本规划仅仅发送数据部分

代码:

module SetData(Rst,SCK,DI,Width,Cycle,PWM);

input SCK,DI,Rst;

output reg [7:0]Width;//脉冲宽度

output reg [23:0]Cycle;//周期

output reg [7:0] PWM;//Pwm数据

reg [7:0]Buff;

reg [7:0] Buff1;

reg [2:0]Stage;//状况变量

reg [5:0]Cnt;

reg Load;

reg INIT;//开端位符号

parameterStatus0= 3b000;//状况界说

parameterStatus1= 3b001;

parameterStatus2= 3b010;

parameterStatus3= 3b011;

parameterStatus4= 3b100;

parameterStatus5= 3b101;

parameterStatus6= 3b110;

parameterStatus7= 3b111;

always @(negedge Rst,negedge SCK)//发生串并转化完结信号(8bit)

begin

if(!Rst) Load<=0;

else if ((!SCK)&&(Cnt==8))

Load<=1;

else Load<=0;

end

always @(negedge DI)//检测开端位

begin

if(SCK==1)INIT<=0;//符号到init 中

else INIT<=1;

end

always @(negedge Rst,posedge SCK,negedge INIT)//状况转化

begin

if ((Rst==0) || (INIT==0))//强制到状况0

begin

Stage<=Status0;

Buff<=0;

end

else if ((SCK==1)&&(Stage==Status0)) begin Stage<=Status1;Cnt<=0; end

else if ((SCK==1)&&(Stage!=Status0))

begin

Buff<={DI,Buff[7:1]};

Cnt <= Cnt+1;

if (Cnt==8)

begin

Cnt<=1;

Stage<=Stage+1;

if (Stage==Status7) Stage<=Status0;

end

end

end

always @(posedge Load,negedge INIT)//组合出需求的数据

begin

if (INIT==0)//如果是开端位,一切数据清零

begin Width <=0;Cycle<=0; PWM<=0; end

else

//begin

case(Stage)//不同状况下的数据输出

//Status0:

Status1: Width<=Buff;//脉宽数据

Status2: Cycle<={ Cycle[23:8],Buff};//周期数据

Status3: Cycle<={ Cycle[23:16],Buff,Cycle[7:0]};

Status4: Cycle<={ Buff,Cycle[15:8],Cycle[7:0]};

Status5: PWM<=Buff;//PWM数据

endcase

// end

end

endmodule

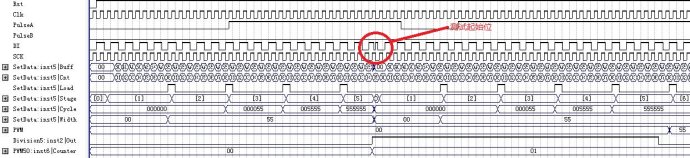

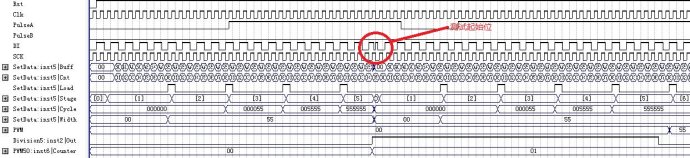

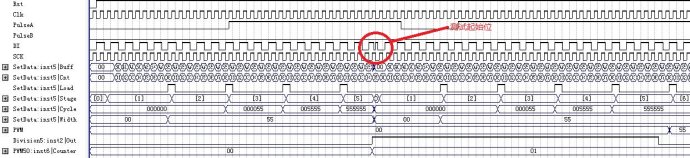

仿真成果

留意图中以为中断了数据发送(经过设置开端位来完成)。

初学verilog言语,用的或许不行标准,主要是不习惯不能在不同进程里对同一个变量赋值的束缚,只好加一个init变量进行信号传递。

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/ziliao/zhudong/233135.html