一、布景

FS2410 开发板上的 ARM 中心为 ARM920T, ARM920T 代表着什么呢? 其实

ARM920T = ARM9 core + MMU + Cache,也便是说 ARM920T 为完成虚拟内存办理供给了硬件

条件,这个硬件条件便是 MMU — 内存办理单元。前面的试验咱们程序里的地址都是直接对应物理地

址,也便是说虚拟地址等同于物理地址,当今凭借 MMU 咱们能够完成虚拟内存办理,程序里边的地址

不再被直接送到地址总线,而是先经过 MMU,由 MMU 来完成虚地址到物理地址的映射。这有什么意义

呢?幻想有这么两个程序,它们有相同的虚拟地址,但由于运转时其虚地址分别被映射到不同的物理地址

,所以它们各行其道、和平共处,而不会产生抵触…有了 MMU 的支撑咱们能够规划出高档的作业体系。

二、意图

怎么启用 MMU, 并完成虚拟地址到物理地址映射正是这次试验的意图。呵呵,你或许现已刻不容缓…

那现在咱们就去探个终究!

三、代码剖析

程序的整个履行流程都体现在 start.S 文件里(曾经不是 head.s文件吗? 呵呵,我把曾经的代码进

行了重构,现在代码看上去更清析–好的架构是很重要的,更便于今后的扩大),start.S里调用的函数有的

是在 .c 文件完成的,必要时我会做相应解说。

1 .text

2 .global _start

3 _start:

4 b reset

5 NOP

6 NOP

7 NOP

8 NOP

9 NOP

10 ldr pc, handle_irq_addr

11 NOP

12 handle_irq_addr:

13 .long handle_irq

14 reset:

15 ldr r0, =0x53000000 @ Close Watch-dog Timer

16 mov r1, #0x0

17 str r1, [r0]

18

19@ init stack

20ldr sp,=4096

21

22@ disable all interrupts

23mov r1, #0x4A000000

24mov r2, #0xffffffff

25str r2, [r1, #0x08]

26ldr r2, =0x7ff

27str r2, [r1, #0x1c]

28

29bl memory_setup @ Initialize memory setting

30bl flash_to_sdram @ Copy code to sdram

31

32ldr pc, =run_on_sdram

33 run_on_sdram:

34ldr sp, =0x33000000

35 bl init_mmu_tlb @ setup page table

36 bl init_mmu @ MMU enabled

37

38msr cpsr_c, #0xd2 @ set the irq mode stack

39ldr sp, =0x31000000

40msr cpsr_c, #0xdf @ set the system mode stack

41ldr sp, =0x32000000

42bl init_irq

43msr cpsr_c, #0x5f @ set the system mode open the irq

44

45ldr sp, =0x33000000 @ Set stack pointer

46bl main

47 loop:

48b loop

(1) 设置间断跳转指令

能够看到程序 4~13 行用来设置间断跳转指令,现在咱们只完成了呼应 IRQ 间断的代

码,所以在第 10 行处放了一条 ldr 加载指令,它的意思是当产生 IRQ 间断时,把

用于呼应 IRQ 间断的函数 handle_irq 的地址加载进 pc 寄存器让程序跳转那里进

行相应处理

(2) 封闭看门狗,程序第 15~17 行

(3) 初始化仓库寄存器体现在第 20 行,之所这么做由于下面会调用一些 C 函数,而 C函

数里的变量当然要保存在仓库里了

(4) 暂时不呼应一切间断: 22~27 行

(5) 第 29 行,初始化内存(内存在这里便是 SDRAM) 慢着…程序不是现已运转在内存里

了吗? 非也,精确点说是运转在 SRAM 里。ARM 启动时会将 Nand Flash(相当于硬

盘)里前 4K 代码加载进 SRAM 里并运转之。那程序大于 4K 怎么办? 呵呵,这正是

下一点要阐明的

(6) 第 30 行,程序本身到内存的般移。咱们的程序大于 4K, 只靠 SRAM 的那不幸的 4K

是运转不开的

(7) 第 32~33 行,跳转到 SDRAM 里履行。咱们的代码现已搬到内存了,64M 的空间够用

的了

(8) 第 34~36 行,设置页表,启用 MMU。这是今日的主角。函数

init_mmu_tlb

init_mmu

界说在 mmu.c 文件里,咱们去看看这个文件里有些什么?

1 /* init MMU page table*/

2 void init_mmu_tlb() {

3 unsigned long vm_addr, idx;

4 unsigned long *tb_base = (unsigned long *)MMU_TBL_BASE;

5

6 for (vm_addr = MEM_START; vm_addr < MEM_END; vm_addr += PAGE_SIZE) {

7 idx = vm_addr >> 20;

8 /* entry: section base, AP=0b11, domain=0b00,cached,write-through*/

9 *(tb_base + idx) = vm_addr|(0x3<<10)|(0<<5)|(1<<4)|(1<<3)|0x02;

10 }

11

12 /* set IO mapped-memory addr for function register*/

13 for (vm_addr = MEM_IO_MAPPED_START; vm_addr < MEM_IO_MAPPED_END; vm_addr += PAGE_SIZE) {

14 idx = vm_addr >> 20;

15 /* entry: section base, AP=0b11, domain=0b00, NCNB*/

16 *(tb_base + idx) = vm_addr|(0x03<<10)|(0<<5)|(1<<4)|0x02;

17 }

18

19 /*

20 * exception vectors

21 * entry: AP=0b11, domain=0b00, cached, write-through

22 */

23 *(tb_base + 0x00000000) = (0x00000000)|(0x03<<10)|(0<<5)|(1<<4)|(1<<3)|0x02;

24 *(tb_base + (0xffff0000>>20)) = VECTORS_PHY_BASE|(0x03<<10)|(0<<5)|(1<<4)|(0<<3)|0x02;

25 }

26

27 void init_mmu() {

28 unsigned long ttb = (unsigned long)MMU_TBL_BASE;

29 __asm__(

30 “mov r0, #0\n”

31

32 /* disable ICache, DCache*/

33 “mcr p15, 0, r0, c7, c7, 0\n”

34

35 /* clear wirte buffer*/

36 “mcr p15, 0, r0, c7, c10, 4\n”

37

38 /* disable ICache, Dcache, TLBs*/

39 “mcr p15, 0, r0, c8, c7, 0\n”

40

41 /* load page table pointer*/

42 “mov r4, %0\n”

43 “mcr p15, 0, r4, c2, c0, 0\n”

44

45 /*

46* write domain id (cp15_r13)

47 * domain=0b11, manager mode, no check for permission

48*/

49 “mvn r0, #0\n”

50 “mcr p15, 0, r0, c3, c0, 0\n”

51

52 /* set control register*/

53 “mrc p15, 0, r0, c1, c0, 0\n”

54

55 /* clear out unwanted bits*/

56 “ldr r1, =0x1384\n”

57 “bic r0, r0, r1\n”

58

59/*

60 * turn on what we want

61 * base location of exception = 0xffff0000

62*/

63 “orr r0, r0, #0x2000\n”

64 /* fault checking enabled*/

65 “orr r0, r0, #0x0002\n”

66 #ifdef CONFIG_CPU_DCACHE_ON

67 “orr r0, r0, #0x0004\n”

68 #endif

69 #ifndef CONFIG_CPU_ICACHE_ON

70 “orr r0, r0, #0x1000\n”

71 #endif

72 /* MMU enabled*/

73 “orr r0, r0, #0x0001\n”

74

75 /* write control register*/

76 “mcr p15, 0, r0, c1, c0, 0\n”

77 : /* no output*/

78 : “r”(ttb));

79 }

程序第 1~25 行是函数 init_mmu_tlb 的完成。其实便是树立一级页表。s3c2410 有四

种内存映射形式: Fault、Coarse Page、Section、Fine Page. 为了简略起见咱们用

Section 形式。ARM920T 是 32 位的 CPU,其虚拟地址空间为 2^32 即 4G。 咱们用

Section 形式来区分这 4G 址址空间,每一个 Section 巨细为 1M,这样就可得到 4K

个 Section。怎样办理这些 Section 呢?经过一张表来记载它们,而这张表被称做页表。

在页表里,用 4 个字节来记载一个 Section 的信息。总共有 4K 个 Section,这样就

要花费 4x4K = 16K 的内存。这用来描绘 Section 的 4 个字节也有个形象的姓名,叫

作描绘符。描绘符的结构又是什么样的呢。来看一下:

Section base address: 段基地址

AP: Access Permission 拜访操控位

Domain: 拜访操控器的索引

C: 被置位时为 write-through (WT)形式

B: 被置位时为 write-back (WB)形式

s3c2410 的 SDRAM 为 64M,其物理地址规模是 0x30000000~0x33ffffff,可区分红

64 个 Section。咱们要完成虚址到物理地址的映射,虚地址是怎么被转化的呢?其实 MMU

将虚地址分红两部分: 索引(index) 和 偏移(offset)。index 便是虚地址的高 12 位,

偏移便是虚地址的低 20 位, MMU 经过 index 在页表里取到相应描绘符,从描绘符里取

到对应 Section 的基地址,再由这个基地址加上偏移 offset 来找出真实的物理地址。

了解了地址映射的基本原理,咱们来剖析上面的代码:

第 6~13 行令 SDRAM 的虚地址和物理地址持平,从 0x30000000 至 0x33ffffff

第 12~17 行设置特别功用寄存器的虚地址,也让它们的虚地址与物理地址持平

第 23~24 行设置间断向量的虚地址,其间高端间断向量地址 0xffff0000 对应到物理

地址0x33f00000

代码中有几个常数,界说如下:

#define MEM_START 0x30000000UL

#define MEM_END 0x34000000UL

#define PAGE_SIZE 0x00100000UL /* page size: 1M*/

#define MEM_IO_MAPPED_START 0x48000000UL

#define MEM_IO_MAPPED_END 0x60000000UL

#define MMU_TBL_BASE 0x30000000UL

#define VECTORS_PHY_BASE 0x33f00000UL

为了了解第 27~79 行的内联汇编究竟做了些什么,咱们先来了解一下协处理器:

在根据 ARM 的嵌入式运用体系中,存储体系经过是经过体系操控协处理器 CP15 来完

成的。怎么设置/读取协处理器的寄存器呢?凭借 MCR/MRC 指令。例如:

MCR P15, 0, R4, C1, C0, 0

将寄存器 R4 中的数据传送到协处理器 CP15 的寄存器 C1 中,其间 R4 为 ARM 寄存

器,寄存源操作数; C1,C0 为协处理器寄存器,为意图寄存器; 操作码1为0,操作码2为0

相应的, MRC 指令将协处理器的寄存器中的数值传送到 ARM 处理器的寄存器中。

好了,咱们来剖析上面的内联汇编代码:

第 32~33 行使数据Cache 和 指令Cache 无效。呵呵, 你没了解过来? 其间原由如下:

CP15 中的寄存器 C7 用于操控 cache 和写缓冲区。它是一个只写的寄存器,运用 MCR 指令

来写该寄存器,具体格局如下:

MCR P15, 0,

其间,

———————————————————————————-

———————————————————————————-

C0 4 等候间断激活0

C5 0 运用无效整个Cache 0

C5 1 使无效指令Cache 中的某块 虚地址

C5 2 使无效指令Cache 中的某块 组号/组内序号

C5 4 清空预取缓冲区0

C5 6 清空整个跳转方针Cache 0

C5 7 清空跳转方针Cache中的某块 生产商界说

C6 0 使无效整个数据Cache 0

C6 1 使无效数据Cache 中的某块 虚地址

C6 2 使无效数据Cache 中的某块 组号/组内序号

C7 0 使数据Cache 和指令Cache 无效 0

C7 1 使无效整个Cache 中的某块 虚地址

C7 2 使无效整个Cache 中的某块 组号/组内序号

C8 2 等候间断激活 0

C10 1 清空数据Cache 中某块虚地址

C10 2 清空数据Cache 中某块组号/组内序号

C10 4 清空写缓冲区0

C11 1 清空整个Caceh 中某块虚地址

C11 2 清空整个Caceh 中某块组号/组内序号

C13 1 预取指令Cache 中某块虚地址

C14 1 清空并使无效数据Cache中某块虚地址

C14 2 清空并使无效数据Cache中某块组号/组内序号

C15 1 清空并使无效整个Cache中某块虚地址

C15 2 清空并使无效整个Cache中某块组号/组内序号

———————————————————————————-

第 35~36 行: 清空写缓冲区

第 38~39 行,使DCache, ICache 及页表的内容无效。体系操控协处理器 CP15 的寄存器 C8就

是用来操控铲除 TLB内容相关操作的。指令格局如下:

MCR P15, 0,

其间

———————————————————————————-

指令

———————————————————————————-

MCR P15,0,Rd,C8,C7,0 0b0000 0b0111 0 DCache,%&&&&&%ache 无效

MCR P15,0,Rd,C8,C7,1 0b0000 0b0111 虚地址 整个Cache 中单个地址改换条目无效

MCR P15,0,Rd,C8,C5,0 0b0000 0b0101 0 整个Cache无效

MCR P15,0,Rd,C8,C5,1 0b0000 0b0101 虚地址 指令Cache 中单个地址改换条目无效

MCR P15,0,Rd,C8,C6,0 0b0000 0b0110 0 整个数据Cache无效

MCR P15,0,Rd,C8,C6,1 0b0000 0b0110 虚地址 数据Cache 中单个地址改换条目无效

———————————————————————————-

第 41~43 行:加载页表的首地址到 CP15 协处理器的寄存器 C2

第 45~53 行:设置拜访操控权限。协处理器 CP15 中 C3 为 DOMAIN ACCESS CONTROL REGISTER,

该寄存器有用位为32,被分红16个区域,每个区域由两个位组成,意义如下:

00:当时级别下,该内存区域不允许被拜访,任何的拜访都会引起一个 domain fault

01:当时级别下,该内存区域的拜访有必要配合该内存区域的段描绘符中AP位进行权查看

10:保存状况

11:当时级别下,对该内存区域的拜访都不进行权限查看

留意第 49 行咱们用的是 “mvn r0, #0” 而非 “mov r0, #0”

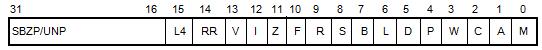

第 59~76 行, 设置并启用 MMU。这几行代码主要是设置了 CP15 的寄存器 C1。C1 是一个操控寄

存器它包含以下功用:

制止/使能 MMU 以及其它的与存储体系相关的功用

装备存储体系以及 ARM 处理器中的相关部分的工作方法

来看一下 C1 寄存器具体是什么姿态:

各操控位意义如下表:

———————————————————————————-

C1中的操控位 意义

———————————————————————————-

M 制止/使能 MMU

A 制止/使能地址对齐查看功用

C 制止/使能整个 Cache

W 制止/使能写缓冲

P 32/26地址形式

D 制止/使能26地址反常查看

L 前期/后期间断模型

B little-endian/big-endian

S 在 MMU 启用时用作体系维护

R 在 MMU 启用时用作体系维护

F 由生产商界说

Z 制止/使能跳转猜测指令

I 制止/使能 Cache

V 低端/高端反常间断向量表

RR 对体系中的 Cache 挑选筛选算法

L4 供给对曾经的 ARM 的版别兼容

bits[31:16] 保存

———————————————————————————-

第 77~79 行: 这是运用嵌入汇编的方法,第 78 行的 “r”(ttb) 表明变量 ttb 的值赋给一个寄

存器作为输入参数,这个寄存器由编译器主动分配。咱们看到第 42 行的 “%0” 被用来表明这个

寄存器。

……呵呵,总算讲完 MMU 这一块了,程序不多,可引出的内容不少!

(9) 第 38~48 行设置 irq 形式和 system 形式下的仓库寄存器,然后程序运转在 system 形式下,

调用 main 函数后回来, 循环并等候间断产生……

这便是 start.S 程序的整个流程,关键是 MMU 怎么设置和启用。其它代码都有具体的注释。我鄙人