摘要 根据直接数字频率组成技能DDS的原理,剖析了影响DDS频率输出的中心要素。在此基础上仿真验证了相位累加器的位数对DDS频率输出的效果。介绍了一种DDS芯片AD9852并根据这种芯片提出了一种雷达回波模仿器的规划,并剖析了DDS芯片的优缺点。该规划可以安稳地发生70 MHz载频的雷达回波,较好地模仿出所需回波。

关键词 DDS;相位累加器;AD9852

直接数字频率组成技能(DDS)是继直接频率组成技能和锁相环式频率组成技能之后的第三代频率组成技能,它的原理是在采样频率必定的条件下,经过操控两次接连采样之间的相位增量来改动所得的离散序列频率,然后经坚持和滤波,仅有回复出该频率的模仿信号。与其他频率组成办法比较,直接数字频率组成器具有频率街边速度快、频率分辩率高、输出相位接连、可编程和全数字化、便于集成等长处。本文在剖析了DDS的基本原理的基础上,提出了一种根据DDS芯片AD9852的雷达回波模仿器的规划。

1 DDS原理

1.1 DDS的基本原理

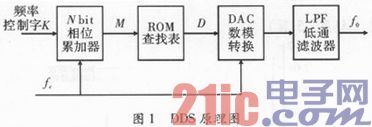

DDS的作业原理是根据相位与起伏的对应联系,经过改动频率操控字K来改动相位累加器(位数为N)的相位累加速度,然后在固定时钟的操控下取样,取样得到的相位值(取相位累加器的高M位)经过相位起伏(ROM查询表法,即在ROM中寄存不同相位对应的起伏序列,然后相位累加器的输出对其寻址)。转化得到相位值对应的起伏序列,起伏序列经过数模转化及低通滤波得到余弦波输出。DDS原理如图1所示。

DDS的中心是相位累加器,它由一个N位相位加法器和一个N位相位寄存器组成。每生成一个时钟脉冲(频率为fc),加法器将频率操控字K与寄存器输出的数组相加,把相加的成果送到寄存器的数据输出端。寄存器将加法器在上一个时钟脉冲效果后发生的相位数据反应到加法器的输入端,以使加法器鄙人一个时钟脉冲的效果下持续与频率操控字相加。这样,相位累加器在时钟脉冲的效果下,不断对频率操控字进行线性相位累加,当相位累加器发生一次溢出时,则完结了一次周期性操作,这便是DDS组成信号的周期,溢出频率是DDS的输出频率f0。输出频率f0与时钟频率fc、频率操控字K以及相位累加器位数的公式为

经过改动频率操控字K,就可改动输出频率的值。由奈奎斯特采样定理可知,DDS的最大输出频率为

fmax=fc/2 (2)

输出信号频率的分辩率即最低的组成频率为

1.2 DDS的功用仿真

经过DDS的原理可知,实践运用中,输出频率f0、时钟频率fc以及相位累加器位数N均已知,则频率操控字K为

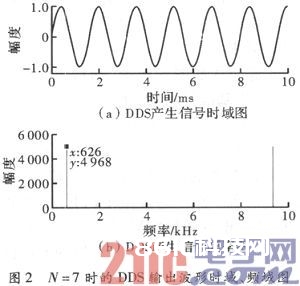

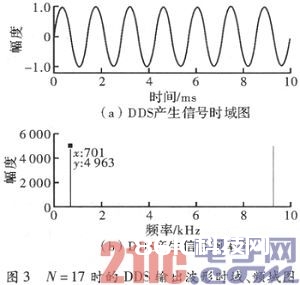

经过Matlab对DDS进行功用仿真,在相同的输出频率f0和时钟频率fc下,改动相位累加器的位数N,则频率操控字K也改动,比较最终经过DDS仿真的输出频率f0。别离设置输出频率为700 Hz,时钟频率为10 kHz,相位累加器的位数别离设置为N=7和N=17,最终实践的输出频率如图2和图3所示。

由图2和图3比较可知,因相位累加器位数的不同,频率操控字K也不同,DDS输出的频率就不同。相位累加器的位数N=7时,实践输出的频率只需626 Hz,间隔预期输出频率700 Hz相差较大;而当N=17时,实践输出的频率为701 Hz,挨近抱负的输出频率700 Hz。因而可知,在相同的采样频率和预期的输出频率下,相位累加器的位数N决议了实践的输出频率。即相位累加器位数N越大,实践输出频率越挨近预期输出频率。

2 AD9852芯片

AD9852数字组成器是一种高集成设备,它选用先进的DDS技能,配上高速、高功能的D/A转化器来完结数字化可编程的组成器功用。当接入准确时钟源时,AD9852能发生一种高安稳度的,频率-相位-起伏-可编程的余弦波,这种波可用于通讯、雷达中作为灵敏的本振信号以及其他多种用处。AD9852的改进型-高速DDS芯片可供给48位频率分辩率。切断到17位的相位保证能发生优质的SFDR.AD9852电路结构,答应输出信号的频率达150 MHz,这使其数字上能以每秒100 MHz的速率调谐成新的频率。

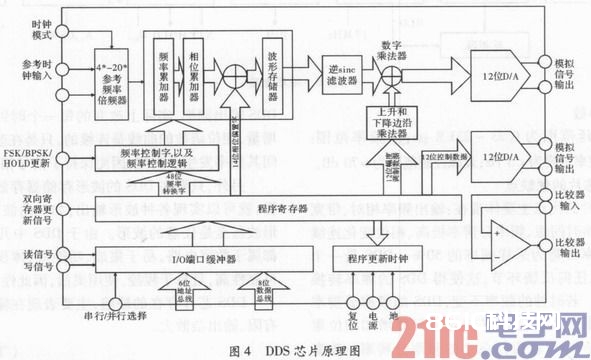

如图4所示,AD9852内部包含一个具有48位相位累加器、一个可编程时钟倍频器、一个反sinc滤波器、两个12位300 MHz DAC,一个高速模仿比较器以及接口逻辑电路。其首要功能特色如下:(1)300 MHz的体系时钟。(2)能输出一般调制信号,FSK,BPSK,PSK,CHIRP和AM等。(3)100 MHz时具有80 dB的信噪比。(4)内部有4~20倍的可编程时钟倍频器。(5)两个48位频率操控字寄存器,可以完结较高的频率分辩率。(6)两个14位相位偏置寄存器,供给初始相位设置。(7)带有100 MHz的8位并行数据传输口或10 MHz的串行数据传输口。

AD9852有40个程序寄存器,对AD9852的操控便是对这些程序寄存器写数据完结的。经过并行总线将数据写入程序寄存器时,实践仅仅暂存在I/O缓冲区中,只需供给更新信号,这些数据才会更新到程序寄存器。AD9852供给内部更新和外部更新两种更新方法。内部更新经过更新时钟计数器完结,当计数器计自减为零后会发生一个内部更新信号;外部更新需求在外部更新管脚上给予一个高电平脉冲。默许的更新形式为内部更新,可以经过设置操控寄存器0x1F的0位进行修正。

3 体系规划

3.1 体系组成

3.2 作业原理

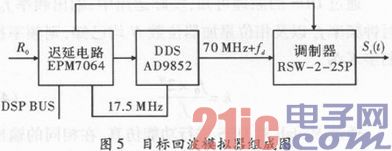

如图5所示,17.5 MHz基准信号经直接数字频率组成器(DDS,选用AD9852)输出70 MHz+fd的方针回波模仿信号,输出经脉冲调制器(选用MINI公司RSW-2-25P)构成方针回波信号St(t)。操控DSP经过总线(BUS)设置回波信号的拖延和DDS输出信号的多普勒频率。

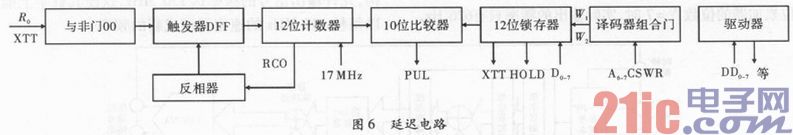

拖延电路组成如图6所示。XTT=1时电路正常作业,间隔同步基准信号R0的前沿使触发器DFF翻转,输出高电平信号令12位计数器退出清零状况开端对17 MHz时钟计数。计数值的高10位(T0-9)与10位拖延时刻锁存器的值DE0-9进行比较,二者持平时输出宽度为0.228 6μs的负脉冲PUL。计数器的进位信号RCO经反相后使触发器复位。译码器对输入的A6、A7、CS、WR信号译码,发生锁存器的数据锁存信号W0、W1。XTT信号为0时,电路封闭,无PUL信号输出。HOLD供AD9852运用,一起对数据总线信号D0-7、WR、RD进行驱动后供AD9852运用。

3.3 体系参数

间隔拖延规模为0.23~233.8μs;fd频率规模:+400 kHz;频率分辩为5 Hz;衰减操控规模为>70 dB。

3.4 DDS芯片的优缺点

DDS芯片的长处首要体现在:输出频率相对、带宽较宽频率转化时刻短、频率分辩率极高、相位改动接连等。输出频率带宽为采样频率的50%。DDS是一个开环体系,无任何反应环节,这使得DDS的频率转化时刻极短。若时钟的频率不变,DDS的频率分辩率便是由相位累加器的位数N决议。只需添加相位累加器的位数N即可取得恣意小的频率分辩率。改动DDS输出频率,实践上改动的每一个时钟周期的相位增量,相位函数的曲线是接连的,仅仅在改动频率的瞬间其频率发生了骤变,因而坚持了信号相位的接连性。

别的,只需在DDS的波形存储器寄存不同波形数据,就可以完结各种波形输出,如三角波、锯齿波和矩形波乃至是恣意的波形。因为DDS中简直一切部件都归于数字电路,易于集成、功耗低、体积小、重量轻、可靠性高,且易于程控,运用灵敏,因而性价比较高。

DDS芯片存在的缺点,首要表现在输出频带规模有限、输出杂散大。

因为DDS内部数模转化器(DAC)和波形存储器(ROM)的作业速度限制,使得DDS输出的最高频有限。因为DDS选用全数字结构,不可避免地引入了杂散。其来历首要有3个:相位累加器相位舍位差错形成的杂散;起伏量化差错形成的杂散和DAC非抱负特性形成的杂散。

4 结束语

在DDS原理的基础上,提出了一种根据DDS芯片的雷达回波模仿器规划。该规划在实践运用中可以安稳地发生所需求的回波。并且,因为DDS芯片所具有的长处,使得其简略便利易于操作。跟着低价格、高时钟频率、高功能的新一代DDS芯片面世,它将在更新范畴得到更广泛的使用。