在图画处理运用开发中,捕获或显现图画的最简略办法之一是运用HDMI(高清晰度多媒体接口)。HDMI是一种可以传输高清数字视频和音频数据的专有规范,被许多显现器和相机支撑并广泛选用。这个特色使得HDMI成为Zynq图画处理运用的抱负接口规范。

在这篇文章中,咱们将向咱们介绍如安在不同方针开发板上运用依据Zynq的HDMI传输。

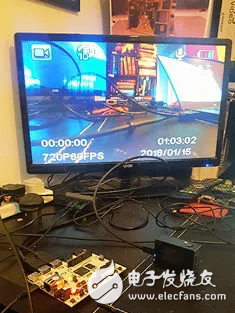

图:Arty Z7 HDMI输入输出事例

依据Zynq开发板对HDMI视频解码包括两种办法:

外部解码(PS端)然后经过I2C总线传到PL端

内部解码(PL端)内部直接解码

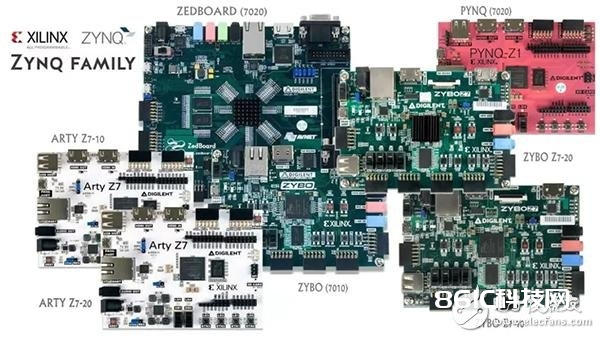

图:支撑HDMI的Zynq开发板

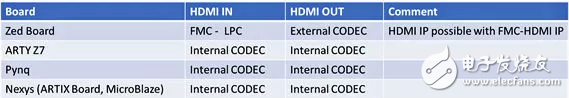

假如开发板运用外部编解码器,则可以运用ADI公司的ADV7511和ADV7611完成发送和接纳。外部HDMI编解码器直接与HDMI衔接器衔接,并生成包括图画、音频数据的TMDS信号(最小化传输差分信号)。

I2C总线,像素数据总线,时序同步信号和像素时钟组成了编解码器和Zynq PL(可编程逻辑)之间的接口。咱们将像素数据,同步信号和时钟直接传送到PL端。运用Zynq PS(处理系统)端的I2C操控器来操控I2C接口,并经过EMIO将Zynq SoC的I2C IO信号传输到PL IO。

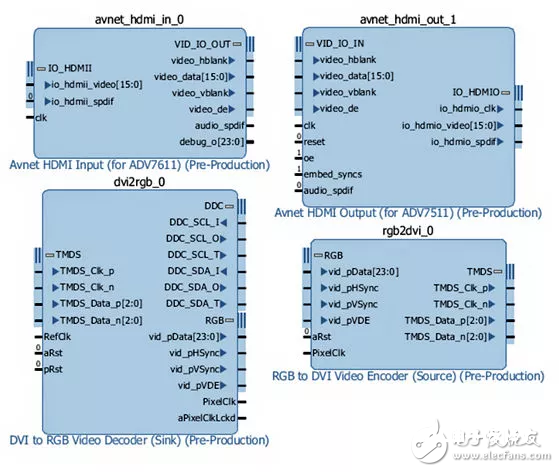

为了简化编码解码器和PL之间的集成杂乱度,这儿介绍两个AVNET所开发的IP核,可经过Avnet GitHub下载( github.com/Avnet/hdl/tree/master/IP )。在图画处理链中,可以把它们放在处理链的最前端和最终端来衔接外部的编解码器。

另一种办法是运用坐落Zynq PL端的内部编解码器。在这种情况下,HDMI TMDS信号直接传输到PL IO,而编解码器用可编程逻辑完成。为了不从头编写这样杂乱的编解码器,可以直接运用 DIGILENT 所供给的两个编解码器IP核(可点击: http://www.digilent.com.cn/community/573.html 附件下载)。在规划中运用这些内核意味着束缚文件中的TMDS信号的IO规范被设置为TMDS_33 IO。

注:此IO规范仅适用于高规模(HR)IO组。

图:本文说到的HDMI IP核

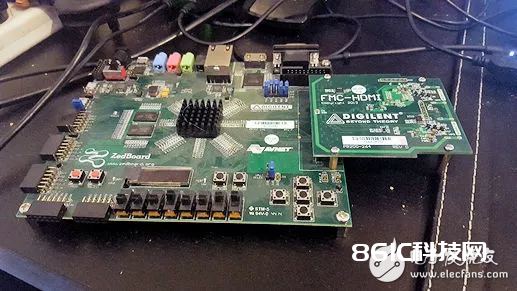

事实上,并非一切Zynq开发板都可以接纳和传输HDMI信号。例如,ZedBoard只供给HDMI输出。假如有必要运用此类开发板接纳HDMI信号,咱们则可以经过FMC接口合作FMC-HDMI子板来进行操作。

Digilent FMC-HDMI子板供给两路HDMI输入,可以运用外部和内部编解码器接纳HDMI数据。在两路输入中,榜首路运用ADV7611,第二路均衡HDMI信号,并直接传输到Zynq PL中解码。这就使得咱们可以演示当运用外部编解码器进行图画传输时,如何将内部和外部编解码器植入ZedBoard。但是,这儿首要咱们需要用电烙铁在J18上焊接一条跳线,这样咱们才可以依据FMC-HDMI子板的要求将ZedBoard上的VADJ设置为3v3。

图:Zedboard + FMC-HDMI子板

最终,友谊提示:虽然咱们在这儿首要评论了Zynq SoC,但上述办法也相同适用于集成了Display Port( www.displayport.org )功用的Zynq UltraScale+ MPSoC哦~