在传统的硬件电路规划中,首要的规划文件是电路原理图,而选用HDL规划体系硬件电路时首要运用HDL编写源程序。

VHDL的首要长处有:

(1)VHDL支撑自顶至下的和根据库的规划方法,而且支撑同步电路、异步电路、现场可编程门阵列器材FPGA(field programmable gate array)以及其他随机电路的规划。

(2)VHDL句子的行为描绘才能和程序结构决议了它具有支撑大规划规划的分化和已有规划再运用的功用,它支撑体系的数学模型直到门级电路的描绘,而且高层次的行为描绘与低层次的门级电路描绘、结构描绘能够混合运用。(3)VHDL的硬件描绘与详细的工艺技术和硬件结构无关,当门级或门级以上的描绘经过仿真查验后,再运用相应的东西将规划映射成不同的工艺,因而电路的规划与工艺的改动是互相独立的。互相的改动不会发生不良影响,而且VHDL硬件描绘言语的实现目标器材的挑选规划广泛,可运用各系列的CPLD、FPGA及各种门阵列器材。

(4)VHDL具有类属描绘句子和子程序调用等功用,关于己完结的规划源程序,能够经过修正类属参数表和函数的方法来改动规划的规划和结构。VHDL具有丰厚的仿真句子和库函数,使得门电路级的功用仿真、查看成为可能,使规划者对整个工程规划的结构和功用的可行性做出决议计划。

(5)VHDL作为一种IEEE的工业规范,使VHDL的规划效果便于重复运用和沟通。这就更进一步推动了VHDL言语的推行及完善。别的,因为其语法严厉,给阅览和运用带来极大的便当。

硬件规划

软件规划

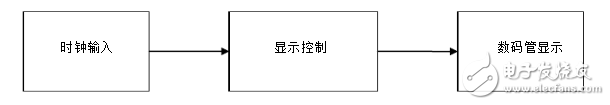

本规划的VHDL程序首要有共有3个部分:分频、数码管扫描进程、显现操控进程。计划原理图如下。

完好程序:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY key IS

PORT(clk : IN STD_LOGIC;

key : in std_logic_vector(7 downto 0);

l : out STD_LOGIC_VECTOR(2 downto 0);

data_o : out STD_LOGIC_VECTOR(7 downto 0);

bell : out STD_LOGIC:=‘0’

);

END key;

ARCHITECTURE an OF key IS

signal clk_1k : std_logic;

signal p : integer range 0 to 7;

begin

process(clk)

variable cnt1 : integer range 0 to 200;

variable cnt2 : integer range 0 to 125;

begin

if clk‘event and clk=’1‘ then

if cnt1=200 then

cnt1:=0;

if cnt2=125 then

cnt2:=0;

clk_1k《=not clk_1k;

else

cnt2:=cnt2+1;