本文依据DSP Builder的VGA接口规划办法,对VGA接口时序和体系规划需求进行了介绍,并在硬件平台下完结一维与二维信号的显现。

VGA接口规范

VGA显像原理

显现器经过光栅扫描的办法,电子束在显现屏幕上有规则地从左到右、从上到下扫描。在扫描进程中,受行同步信号操控,逐点往右扫,完结一行扫描的时刻倒数为行频;一起又在行同步脉冲期内回到屏幕的左端,从上往下构成一帧,在笔直方向上受场同步信号操控,完结一帧的时刻倒数为场频。图画的显现进程即为在电子束扫描进程中,将地址与图画的像素顺次对应,每一个被寻址的像素只取得其本身的操控信息,而与周围的像素不发作搅扰,然后能够显现安稳的图画。

VGA接口是显现卡上输出模仿信号的接口,也叫D-Sub接口。这种接口上面共有15个针孔,分红3排,每排5个,经过模仿VGA接口显现图画的作业原理,将计算机内部以数字办法生成的显现图画信息,经过显卡中的ADC转变为R、G、B三基色信号和行、场同步信号,经过电缆传输到显现设备中。

VGA时序

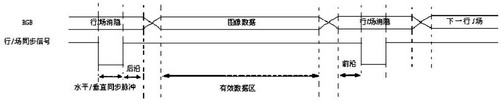

VGA的时序包含水平时序和笔直时序,且两者都包含的时序参数有:水平(笔直)同步脉冲、水平(笔直)同步脉冲完毕到有用显现数据区开端之间的宽度(后沿)、有用显现区宽度、有用数据显现区完毕到水平(笔直)同步脉冲宽度开端之间的宽度(前沿)。水平有用显现区宽度与笔直有用显现区宽度逻辑与的区域为可视区域,其他区域为消隐区。

一行或一场的时序信息如图1所示。

图1 行/场时序图

依据现在的显现器性能参数,以LG 505E为例,其最大分辨率已可到达1024×768@60Hz,水平扫描频率30kHz”54kHz ,笔直扫描频率50Hz”120Hz,带宽75MHz。

依据DSP Builder的VGA接口规划办法

本规划需求完结的功用包含发作VGA时序以及依据VGA接口的信号显现。规划契合VGA接口规范的接口体系,在该体系下可显现一维矢量信号与二维图画信号,并表现体系的可集成性,将该接口集成到SOPC体系中。

体系时钟确认

依据体系时钟计算公式:

时钟频率=(行像素数+行消隐点数)×(一场行数+消隐行数)×刷新率。

关于规范的VGA接口时序640×480@60Hz而言,时钟频率为800×525×60=25.175MHz。

在本规划中咱们选用1024×768@60Hz的XGA显现办法,因而体系的时钟频率PixelClk=1344×806×60=64.99MHz。

状况机规划

由VGA时序可规划有限状况机来完结时序信号,以本规划1024×768@60Hz为例,关于行同步信号规划四个状况,即行同步脉冲信号区(horsync)、后沿区(backporch)、数据区(video)以及前沿区(frontporch)。用计数器hcnt的值来区别各阶段信号,最大记数值为1344。场同步信号也规划成如上四个状况,当完结一行的扫描后场计数器vcnt开端计数,因而一场能够有多行。

VGA DAC芯片及相应信号的生成

一般的VGA DAC芯片需求输入相应的驱动信号才干作业,包含时钟信号、同步信号、有用显现区信号等。体系所用DAC芯片为FMS3818,其信号包含时钟与数据信号(RGB)输入、操控信号输入(sync与blankn)以及RGB信号DA输出。行同步与场同步信号与经VGA DAC发作的RGB数据信号同时输出到VGA接口,驱动CRT显现。在本规划中时钟信号65MHz、同步信号为horsync与versync相与发作,有用显现区信号为行与场的有用数据区信号相与发作。

一维矢量信号显现办法

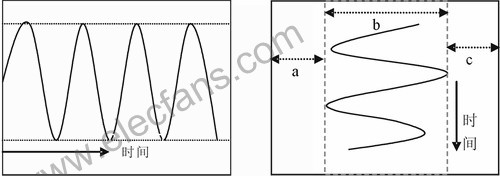

在二维的空间中显现一维矢量信号,惯例显现办法能够是将一维信号从左至右显现,如图2(a)所示,就如在一般的示波器上调查到的相同。这样,在VGA显现时,一行扫过多个采样点,需把要显现的采样点方位计算出来,当行信号扫过期,把采样点的值赋给像素点,就完结了信号的显现。而关于接连的一维信号,因为行频比场频高,图2(b)的显现办法愈加合理。为此,将一维信号的时刻轴映射到笔直方向上,幅值映射到水平方向上,当行扫描信号扫过一行时,映射一维信号的一个采样点,即一行信号对应一个像素,当完结一行信号后接着回扫,开端扫下一行。一般情况下,场频确认后,就能够依据一维信号的频率确认出一场能够显现的周期数,当完结一场信号后,在屏幕上就显现一帧图画。

在详细完结时,需求对一维正弦波信号的参数作两点操控:操控正弦波的频率,确保一行扫描对应一个采样点;操控正弦波的起伏,将其操控在1024×768的有用显现区域中。

对正弦波频率来说,假如频率太高,一行会扫到多个采样点;假如频率太低,一整屏无法显现一个完好周期的信号。在本规划中,用一个较低的采样时钟操控正弦波的采样,正弦波存放在一个查找表中。假如要在一屏中显现n个周期的正弦信号,那么需求的采样频率fs=刷新率×n×查找表中一个周期的点数。

操控正弦波起伏即让正弦波的最大值不能超出屏幕的显现区。VGA有用显现宽度为1024,则屏幕两头的闲暇部分宽度(图2(a)和(c))都为100。

(a) (b)

图2 一维正弦波VGA显现示意图

二维图画信号的显现办法

二维图画的显现进程较一维信号简单完结。对二维图画,能够将二维图画信号转变成一维像素序列。在屏幕显现区域内,当行与场同步信号扫过期,将该像素点对应的RGB值进行赋值,就能够完结二维图画的显现。关于本规划,VGA时序为1024×768形式,图画的像素数在这个范围内能够彻底在屏幕上显现,不会发作像素丢掉。假如图画比较小,还能够将图画操控在屏幕的恣意区域内。因为图画巨细受存储空间约束,假如想要完结更高像素点的图画,就必须借用外部的SRAM或SDRAM来做图画缓存。

Avalon MM接口操控

在DSP Builder中,Altera供给了本规划与SOPC的接口——Avalon MM接口。

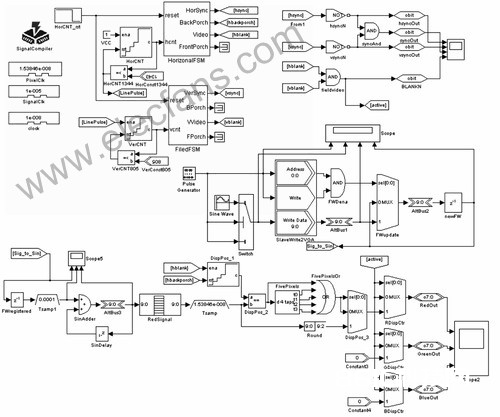

Avalon MM接口界说的接口信号首要有片选、读使能、写使能、地址,以及数据等。依据外设的逻辑,选用不同的接口界说信号,经过这些信号Avalon主端(CPU)能够向挂在Avalon总线上的从端外设写地址与数据信号,Avalon主端外设也能够自动去获取Avalon总线上的SRAM或SDRAM中的数据。不管是主传输仍是从传输,都需求契合Avalon总线的读写时序才干建议一次正确的数据传输。能够运用Avalon MM接口将DSP Builder中规划的模块做成自界说外设。NiosⅡ CPU就能够运用Avalon总线与DSP Builder中发作的自界说外设进行通讯,在本规划中对集成到SOPC体系上的VGA接口的地址赋值为0x1后,数据写入0x1,VGA接口操控器接收到数据,就会依据规划发作VGA时序信息及RGB信号,在屏幕上显现图画。图3为整个一维信号VGA显现体系的结构图。

图3 体系结构图

仿真与硬件验证

本规划在2C70 DSP硬件开发平台下验证。

借助于DSP Builder中的Signal Complier模块,能够简单地将规划完结的体系直接转化成RTL级的硬件描绘言语,在QuartusⅡ下完结VGA时序的验证与正弦波信号的下载与显现。

从显现器上硬件仿真成果来看,正弦波的起伏在有用的显现区域内呈周期性改变,因而当显现器与VGA口的J21相连时,屏幕上正弦波起伏在规划的范围内显现,一幅屏幕所显现的周期数和DSP Builder中所设定的共同。在此基础上还能够调整正弦波的采样频率,操控正弦波的显现频率与起伏巨细,完结示波器的功用,调查FPGA内部的信号。

结语

跟着VGA接口的广泛运用,这种结合FPGA与DSP Builder的体系级规划办法现已展示优势。从整个规划流程来看,体系的灵活性强,可靠性高,规划周期大大减缩,本钱下降,且体系的可扩展性强。未来,VGA接口的图画与视频监控体系使用将会很有商场。