前语

在数字录像、数字监控等领域内,人们一般只对场景内存在的物体运动感兴趣。在这种状况下,需求对输入的视频信号进行预处理,辨认场景中是否存在物体运动,也便是进行运动检测,然后再决议是否做进一步的处理,例如录像、报警等。关于录像体系,经过运动检测,能够防止不必要的数字录像,有用地削减体系所需存储空间;一起能够加速检索速度,进步材料有用性。关于监控体系,运动检测是一种监督场景信息的有用手法。

1 操控器原理图

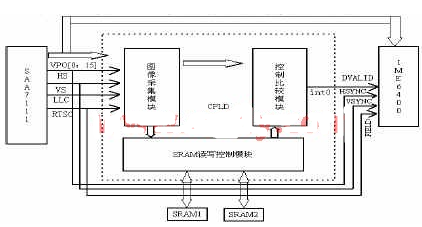

操控器CPLD的规划及完结是运动检测的中心部分,它需求对外围的器材进行集中操控和处理。本文选用了Altera公司的CPLD EPM7128S84-15,选用VHDL作为硬件描绘言语,可是所编写的VHDL源程序已然适用于CPLD器材,又适用于FPGA器材。CPLD操控器规划框图如图1.1所示,操控器的全体结构大体上可分为图画收集操控模块、SRAM读/写操控、操控比较模块等三个部分。

Fig1.1 System diagram

图1.1 体系原理框图

2 图画收集与操控硬件部分

图画收集部分选用了Philips公司的视频A/D转化芯片SAA7111A,SAA7111A是Philips公司推出的一款功用强大的视频信号预处理芯片,最基本的功用是模/数转化,输出的是长宽比为4:3和16:9数字视频信号,契合ITU601规范。在我国,一般选用的都是4:2:2采样格局、PAL制式、长宽比为4:3的数字电视信号。

文中用到的CPLD是Altera公司的EPM7128SLC84-15,它具有128个宏单元、7.5ns的延时。SRAM芯片是ISSI公司的IS61C1024L-12,其容量为128K×8bit,具有10ns的延时。CPLD检测到运动后,经过中止,要求IME6400对信号做进一步处理。其体系结构图如图1.1所示。

SAA7111A输出的是长宽比为4:3和16:9的数字视频信号,输出信号包含消隐期在内,每帧数据扫描625行,每行抽样864个象素,因而总的分辨率是864×625。一帧数据分作奇偶两场,从上一帧的624行到本帧的310行是奇场,其间上帧624行到本帧22行是奇场消隐期,从23行到310行是奇场有用行;从本帧311行到623行是偶场,其间311到335行是偶场消隐期,336到623行为偶场有用行。

在一帧图画数据的收集进程中,最重要的便是对一帧图画数据开端和完毕时刻的判别。在研讨了SAA7111A所供给的同步信号(奇偶场标识信号)RTS0、场同步参阅信号(VREF)、行同步参阅信号(HREF)的时序联系的基础上,用状态机完结了对收集进程起止点的准确操控。RTS0信号的上升沿标识一帧新图画的起点,VREF信号为高电平对应场图画正程扫描时的有用像素行期间,在有用像素行期间,HREF信号为高电平对应像素有用采样时刻。只对一帧抽样数据进行缓存,在对第二帧数据进行抽样时读取榜首帧中与此时抽样的数据相对应的缓存数据,并将两者进行比较,用一个计数器记载比较成果,假如差值超越阈值,计数器加一,不然不加。当这个计数值超越某一个规则数值的时分,就以为输入视频数据中存在着物体运动。这样做的优点是需求的缓存区较小,并且CPLD能够独自对数据进行处理,进步运动检测模块的独立性,运动检测模块能够独自调试。

3 图画收集操控软件部分

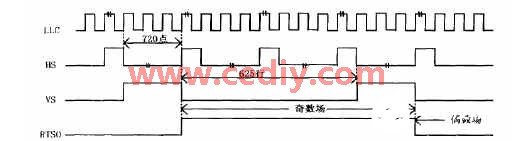

体系中PAL制式下SAA7111A输出的参阅信号时序如图1.2所示。其间LLC是像素时钟信号,时钟频率为27MHZ,高电平表明输出一像素点;HS为行同步信号,其上升沿表明行消隐期开端,下跳沿标志着新的一行采样数据行将开端;VS为场同步信号,其上升沿表明场消隐期开端,下跳沿标志着新的一场采样数据行将开端;RTS0为奇偶场标志信号,RTS0为高电平时,输出奇数场采样数据,RTS0为低电平时,输出偶数场采样数据。

Fig1.2 SAA7111A timing diagram

图1.2 SAA7111A输出的参阅信号时序图

体系中SAA7111A的初始设定为:一路模仿视频信号输入、自动增益操控、625行50Hz PAL制式、YUV4:2:2 (16bit)数字视频信号输出、设置默许的图画对比度、亮度及饱和度。

读/写操控模块的主要功用便是完结操控SRAM的读写。下面给出完结以上进程的一部分VHDL程序。

Sram_write_control process store_field valid spclk2 line_counter

begin

wriTIng《=valid and spclk2 and spclk and store_field and line_counter0

end process

Sram_read_control process compare_field valid spclk2 line_counter

begin

reading《=valid and compare_field and spclk2 and line_counter0

end process

这两个进程用于操控SRAM的读写信号,reading和wriTIng正好和SRAM的读写信号反相。Valid变量指示当时输入的行是否为需求采样的有用行,spclk是象素数据同步脉冲,spclk2是它的二分频,用于指示当时输入数据是否为亮度重量Y。line_counter0=1表明奇数行。Store_field和compare_field别离指示本场数据是否需求保存或许需求比较。

update_data_bus process store_field valid ccd_data

begin

if store_field=’1’and valid=’1’then

data_sram《=ccd_data

else

data_sram《=”ZZZZZZZZ”

end if

end process

compare_data进程在抽样的距离(输入为色度重量Cr或许Cb时)对前后两次抽样的数据进行比较,假如比较成果超越答应值,计数器pixels加1,不然不加。

moTIon_detect process pixels

begin

if pixels》max_pixels then

int0《=’1’

else

int0《=’0’

end if

end process

max_pixels是一个阈值,表明一帧数据中答应呈现的不相等抽样数据的最大数目,当计数器pixels超越max_pixels时,就以为检测到了物体运动,CPLD将int0输出管脚置高,向处理器恳求中止。这儿max_pixels取600,它能够依据需求设置恰当的值。

当然这种检测办法自身也有不足之处,最主要的一点是实践检测到的仅仅摄像头前光线亮度的改变,不能智能地判别引起这种改变的原因,也不能判别运动物体的形状。另一方面,从试验成果来看,有时分会呈现误判;当运动物体离摄像头比较远时,检测的灵敏度也会下降,呈现漏判。误判和漏判是一对对立,在实践使用中需求依据实践状况重复调试,选出最佳的阈值,削减这两种状况的产生。

4 定论

本文作者立异点是结合在体系可编程技能,选用CPLD/FPGA芯片EPM7128S84-15规划图画收集与处理操控器。该规划现在正在我院安全防备监控体系中试用,作用杰出。

责任编辑:gt